B. sharing plls for multicore designs – Altera POS-PHY Level 4 IP Core User Manual

Page 113

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

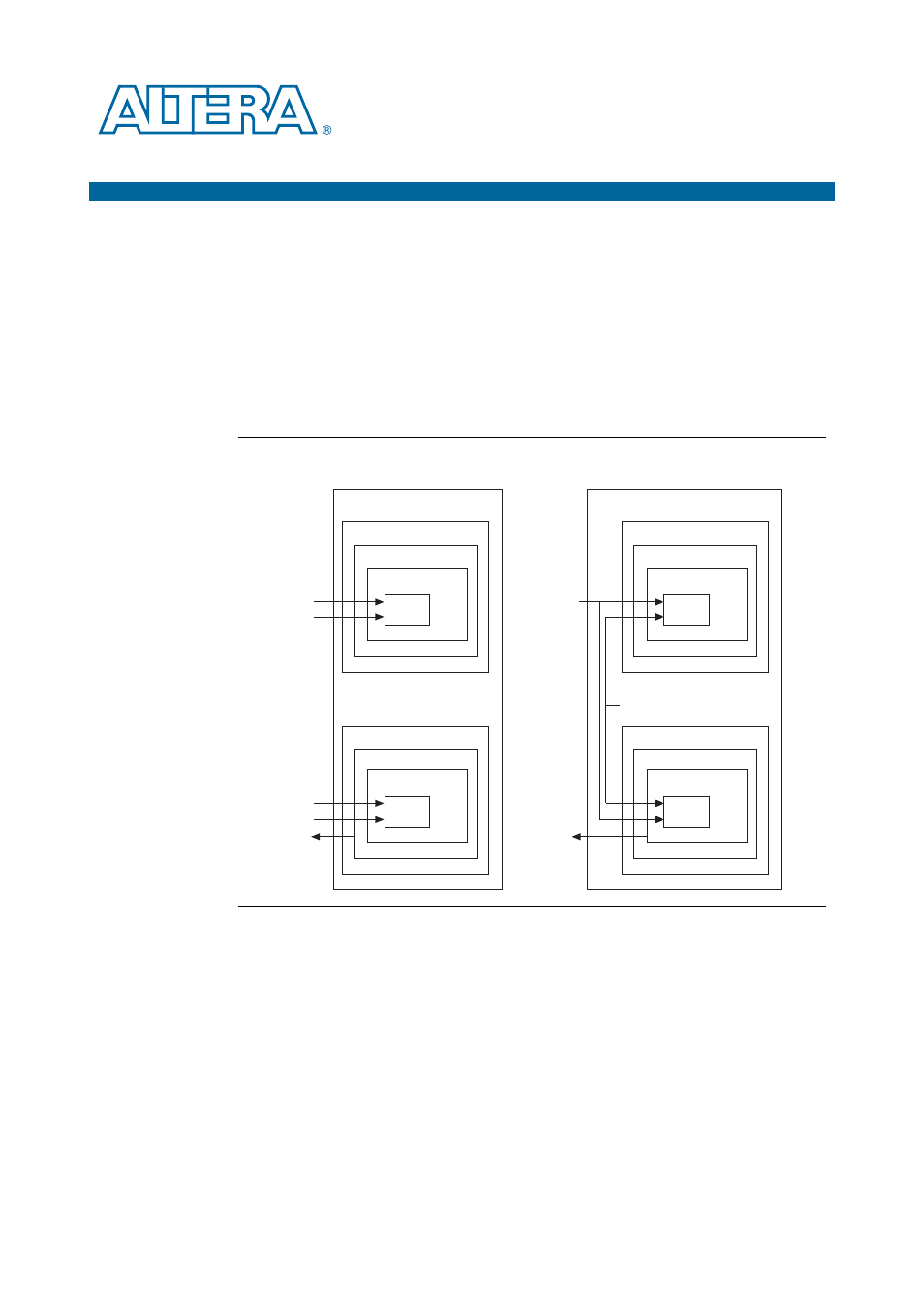

B. Sharing PLLs for Multicore Designs

This appendix explains how to share a PLL between one receiver and one transmitter

POS-PHY 4 IP core and between two transmitter cores.

shows how to connect the reset and the rdclk and trefclk signals when

you share a PLL between a receiver and transmitter core.

1

shows two PLLs, the Quartus II software optimizes the PLL

instance as if it is one PLL.

To share the PLL, follow these steps:

1

The LVDS data rates must be the same for each core.

1. Create a new Quartus II project, but call the project name and the top-level entity

names different names.

2. Create your receiver core.

3. Create your transmitter core.

Figure B–1. Connect rdclk and trefclk Signals

tdclk

altlvds Megafunction

<variation name>_tx_core.v

<variation name>.v

PLL

altlvds Megafunction

<variation name>_rx_core.v

<variation name>.v

rdclk

reset

PLL

rdclk

PLL

reset

trefclk

PLL

reset

Top-Level Entity

Separate PLLs

tdclk

altlvds Megafunction

<variation name>_tx_core.v

<variation name>.v

trefclk

altlvds Megafunction

<variation name>_rx_core.v

<variation name>.v

reset

Top-Level Entity

Shared PLL