Requirements for rxsys_clk – Altera POS-PHY Level 4 IP Core User Manual

Page 49

Chapter 4: Functional Description—Receiver

4–11

Clock Structure

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

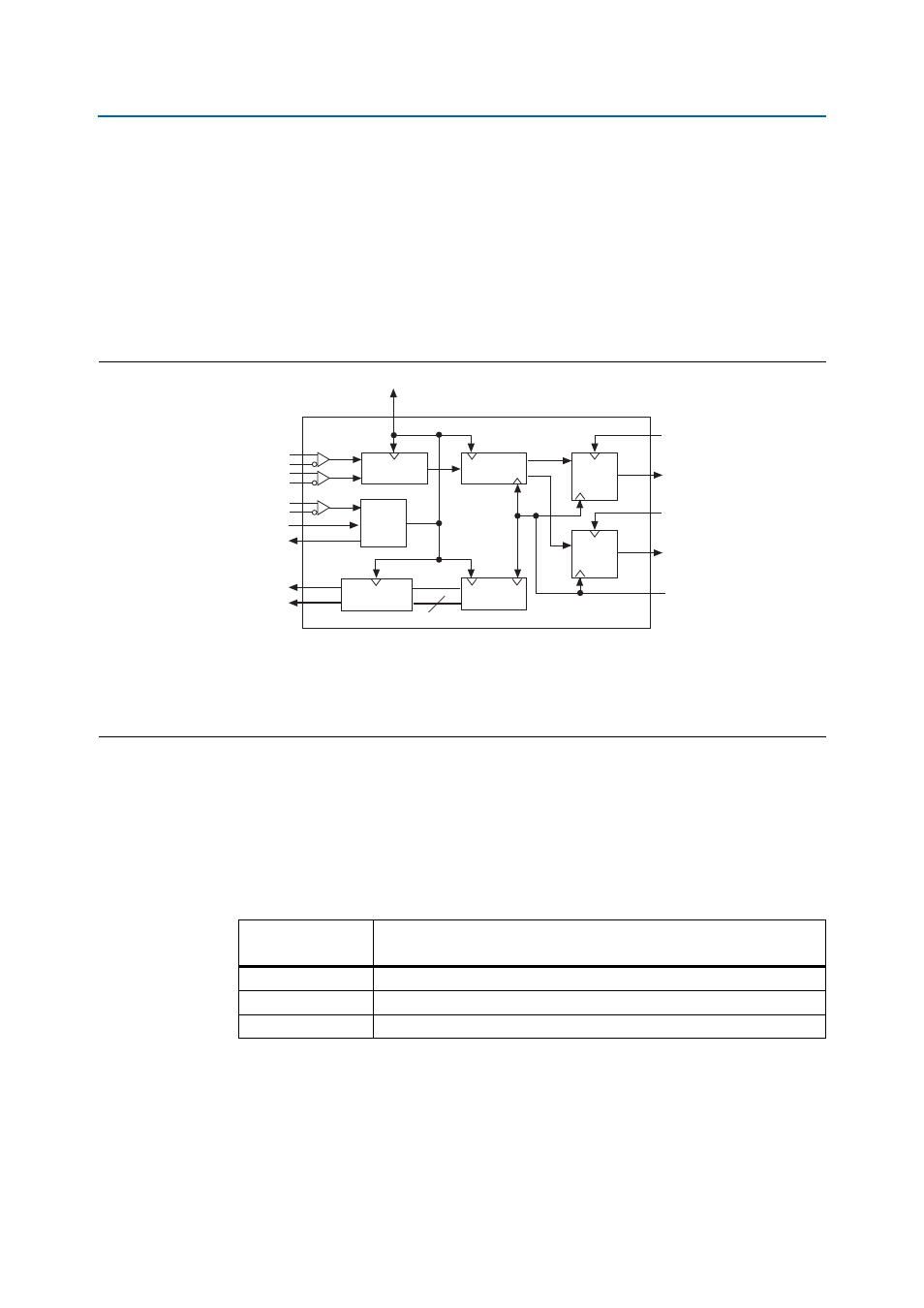

In 32-bit (quarter-rate) SPI-4.2 mode, all the above clocks exist. The maximum

frequency of the clocks depends on ALTDDIO_IN limitations. To minimize clock

skews, the rdclk goes into a PLL where it generates rdint_clk (×1). The PLL is

required to provide 90 phase shift, so the ALTDDIO_IN IP core samples in the centre

of the data eye. A typical system may have a rdint_clk of 100 MHz, of which the SPI-

4.2 data rate is 200 Mbps. Most of the quarter-rate receiver IP core runs off rdint_clk,

including all data path processors and the write side of the FIFO buffer.

Figure 4–5

shows the clocking structure used by the receiver IP core, for 32-bit (quarter-rate

mode) variations that use the ALTDDIO_IN IP core.

Requirements for rxsys_clk

The IP core’s protocol logic and all Atlantic FIFO buffers share a common clock called

rxsys_clk

that clocks both the write and optionally the read side of the Atlantic FIFO

buffers.

Table 4–2

shows guidelines for the frequency of rxsys_clk.

f

For detail on the optimum setting of rxsys_clk, refer to

Figure 4–5. Clock Layout Diagram (Quarter Rate)

Notes to

Figure 4–5

:

(1) rxsys_clk is internally connected to rdint_clk in 32-bit shared buffer with embedded addressing mode variations.

(2) The single clock mode removes the separate Atlantic clocks.

(3) The embedded address mode has only one buffer; the individual buffers mode can have more than one buffer.

(4) In 32-bit (quarter-rate) SPI-4.2 mode, this PLL only provides a phase shift for the incoming rdclk.

ALTDDIO_IN

ALTDDIO_OUT

EPLL

(Note 4)

Status

Processor

Data

Processor

Atlantic

Buffer 0

Atlantic

Interface 0

a0_arxclk

aN_arxclk

(Note 2, 3)

rdclk

ctl_rx_pll_areset

stat_rx_pll_locked

rdat[15:0]

rctl

rxsys_clk

(Note 1)

rdint_clk

rsclk

rstat[1:0]

Atlantic

Buffer N

Atlantic

Interface N

2

Table 4–2. Frequency Guidelines—rxsys_clk

Data Path Width

(Bits)

Worst Case Frequency Requirement

32

1.0 × rdint_clk

64

1.25 × rdint_clk

128

1.6 × rdint_clk