Altera POS-PHY Level 4 IP Core User Manual

Page 62

4–24

Chapter 4: Functional Description—Receiver

Signals

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

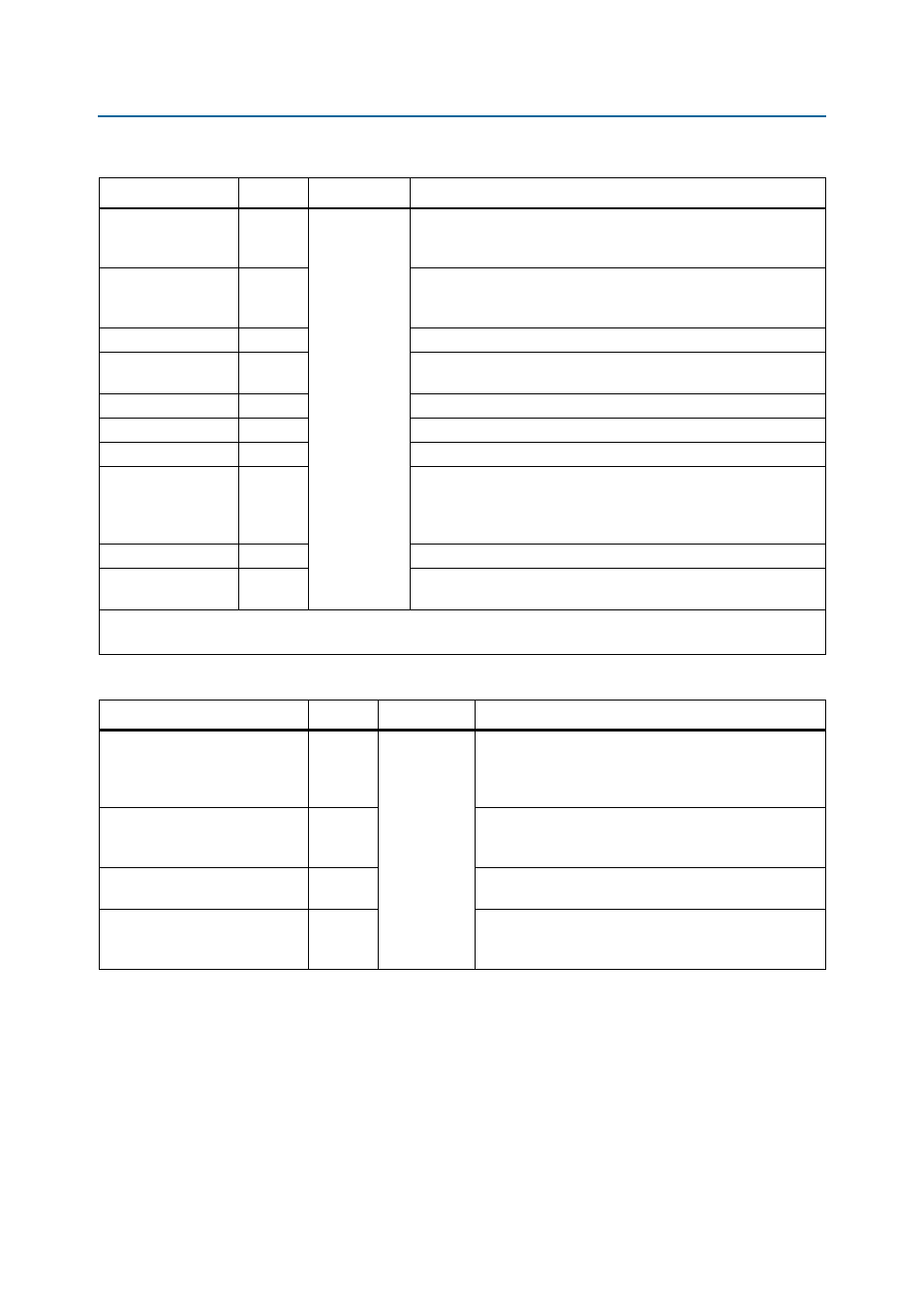

Table 4–7. Atlantic Receive Interface (Slave Source)

(Note 1)

Signal

Direction

Clock Domain

Description

aN_arxclk

Input

aN_arxclk

Atlantic clock (one for each Atlantic interface). This input is absent

and internally connected to rxsys_clk if a single clock domain is

selected. Signals prefixed with aN_ are synchronous to this clock.

aN_arxdav

Output

Atlantic data available (one for each Atlantic interface). Asserted when

the Atlantic FIFO buffer has at least ctl_ax_ftl bytes available to

read.

aN_arxena

Input

Atlantic enable (one for each Atlantic interface).

aN_arxdat[n:0]

Output

Atlantic data bus (one for each Atlantic interface). The width is set by

the Atlantic interface width parameter.

aN_arxval

Output

Atlantic data valid (one for each Atlantic interface).

aN_arxsop

Output

Atlantic start of packet (one for each Atlantic interface).

aN_arxeop

Output

Atlantic end of packet (one for each Atlantic interface).

aN_arxmty[n:0]

Output

Atlantic empty signal (one for each Atlantic interface). Number of

invalid octets on the upper bits of the Atlantic data bus (aN_arxdat).

Valid only when aN_arxeop is asserted. The width is log2(Atlantic

width/8)

.

aN_arxerr

Output

Atlantic error (one for each Atlantic interface).

aN_arxadr[7:0]

Output

Atlantic port address (one for each Atlantic interface). Only present

for the shared buffer with embedded addressing mode.

Note to

Table 4–7

:

(1) N is equal to the number of ports for the individual buffers mode; N is equal to zero for the shared buffer with embedded addressing mode.

Table 4–8. Atlantic FIFO Buffer Control and Status (Part 1 of 2)

Signal

Direction

Clock Domain

Description

ctl_ax_ftl[n:0]

(1)

Input

aN_arxclk

FIFO buffer threshold low determines when to inform the

user logic that data is available via the aN_arxdav signal.

This threshold applies to all buffers. Units are in bytes.

Only change at reset.

ctl_ax_fifo_eopdav

Input –

Static

reset

Assert to turn on dav when there is an end of packet

below the FTL threshold. Value applies to all Atlantic

buffers. Only change at reset.

err_aN_fifo_parityN

Output

Indicates that the FIFO buffer has detected a parity error

(one for each Atlantic buffer).

stat_aN_fifo_emptyN

Output

Indicates that the FIFO buffer has underflowed. Asserted

for one cycle if a buffer read fails because the buffer is

empty (one for each Atlantic interface).