Altera POS-PHY Level 4 IP Core User Manual

Page 116

C–2

Appendix C: Optimum Frequency for rxsys_clk

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

If you increase the LVDS data rate to 820 Mbps (rdint_clk = rsclk = 102.5 MHz), the

new minimum required rxsys_clk frequency from restriction (a) is:

(4/3.125) × 102.5 = 131.2 MHz

and from restriction (b) is:

102.5 × 4/3 = 136.667 MHz

If you do not want to increase the rxsys_clk frequency, you can increase the status

frame length. By setting the calendar multiple to 2, the required frequency from

restriction (b) is

Status frame length = 4

rxsys_clk

frequency 102.5 × 5/4 = 128.125 MHz

By changing the calendar multiple to 2, the required minimum rxsys_clk frequency

is 131.2 MHz (from restriction (a)).

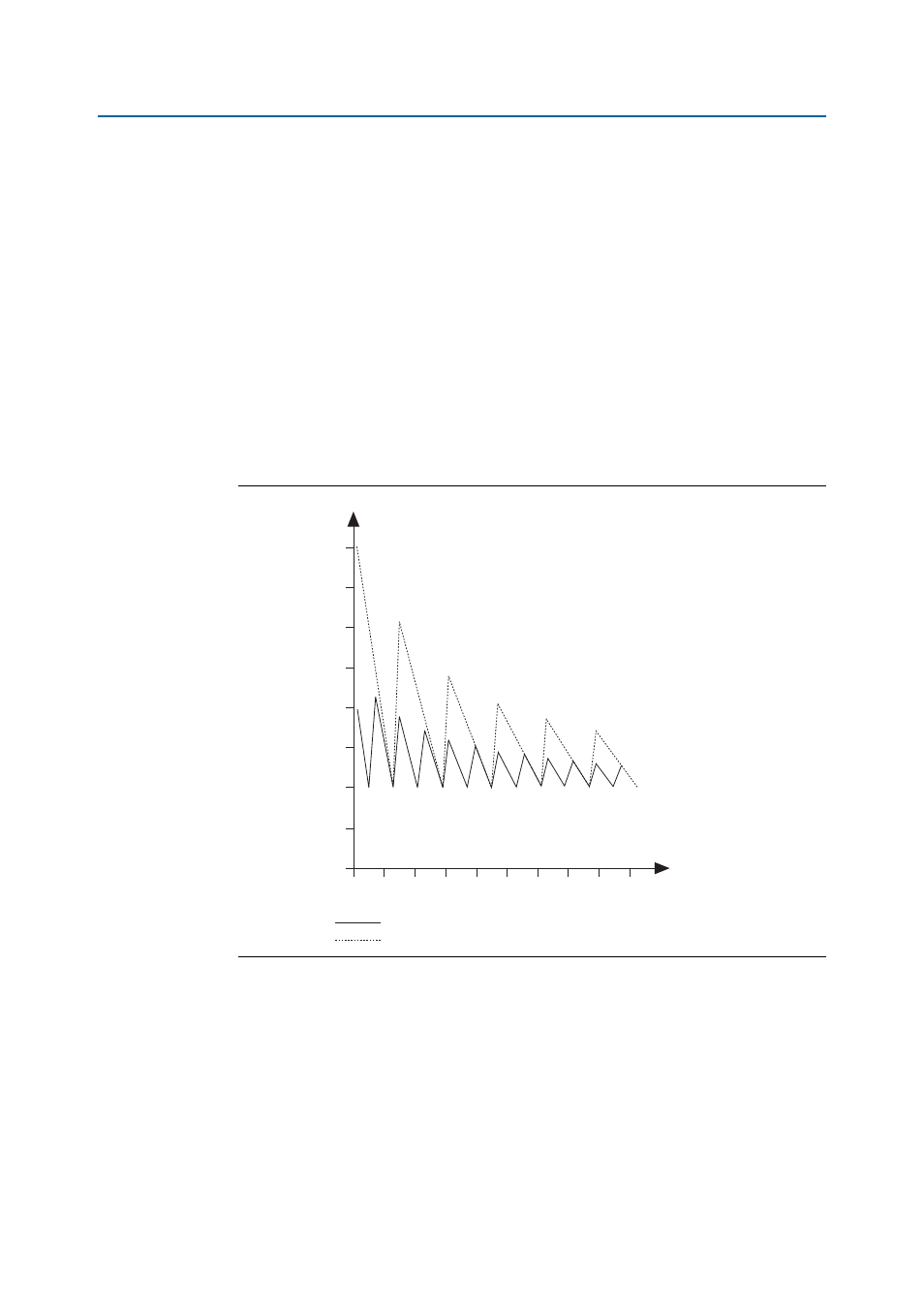

Figure C–1. Minimum Frequency Ratio versus Packet Size

Ratio

Packet Size

(Bytes)

0.8

MegaCore Width = 64

0.9

1.0

1.1

1.2

1.3

1.4

1.5

1.6

20

30

40

50

60

70

80

90

100 110

MegaCore Width = 128