A. start-up sequence – Altera POS-PHY Level 4 IP Core User Manual

Page 107

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

A. Start-Up Sequence

This appendix applies to any SPI-4.2 transmitter and receiver pair, where at least one

is an Altera

®

POS-PHY Level 4 IP core.

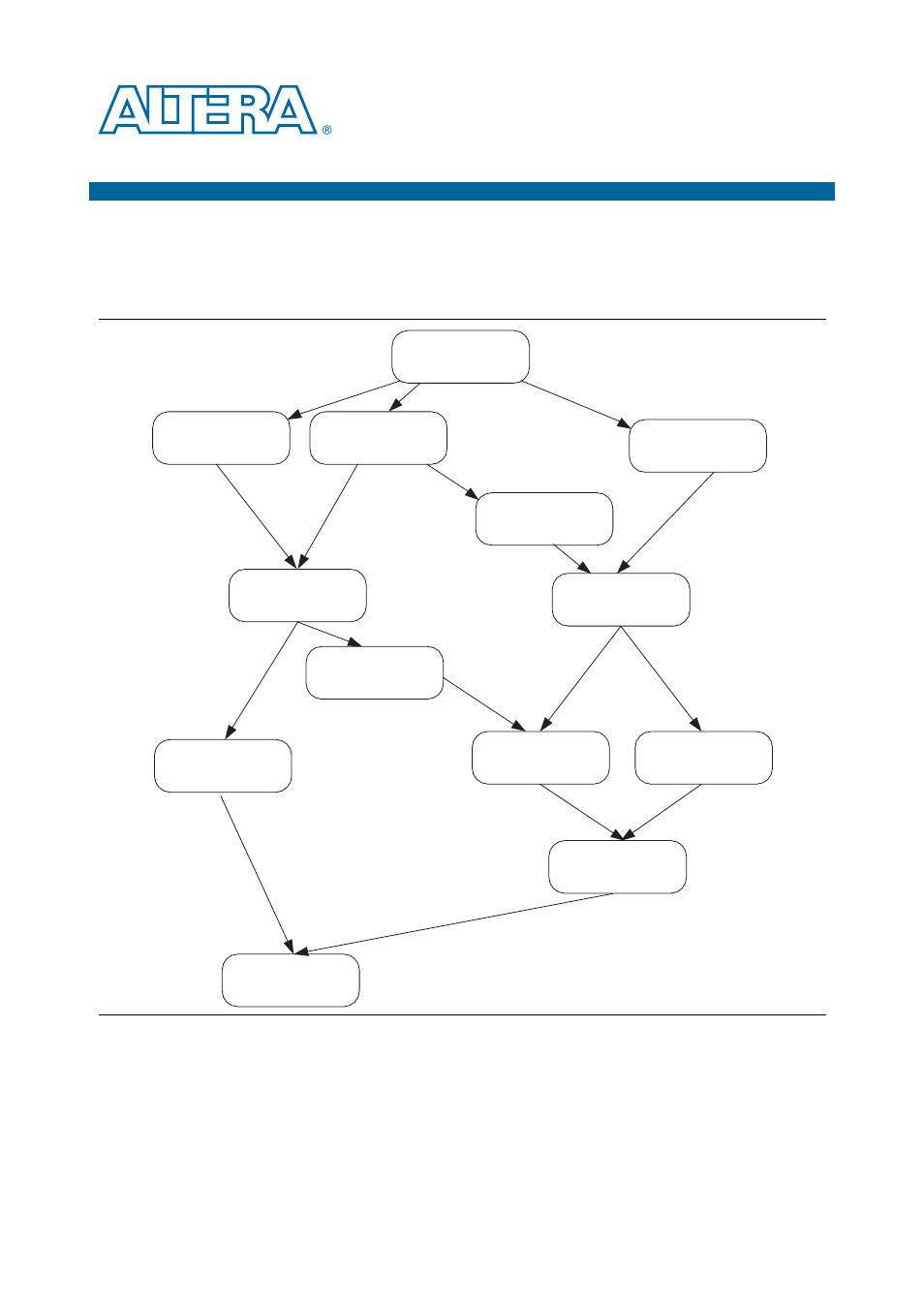

The startup sequence combines clock stabilization, reset, and configuration with the

training and framing aspects of the SPI-4.2 protocol as shown in

Figure A–1 on

page A–1

. Details of each event as they happen in the POS-PHY Level 4 IP core are

listed in

Table A–1

, but similar events should happen in other SPI-4.2

implementations.

Figure A–1. Start-Up Sequence Flowchart

TX system clocks

stabilize

(2a)

TX PL4 clocks

stabilize

(2b)

RX system clocks

stabilize

(2a)

Release TX core reset

and

disable status FSM

(3)

TX sends training

(3)

RX PL4 clocks

stabilize

(2b)

RX DPA

stabilized and trained

(5a)

Release RX core reset

and

disable status FSM

(3)

Configure TX function

and

enable status FSM

(4)

Configure RX function

and

enable status FSM

(4)

RX ready

Sends status frames

(6)

TX frames on status

TX ready

(6)

Power up

Assert all resets

RX sends 'b11 status

(1)