Altera POS-PHY Level 4 IP Core User Manual

Page 90

5–20

Chapter 5: Functional Description—Transmitter

Signals

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

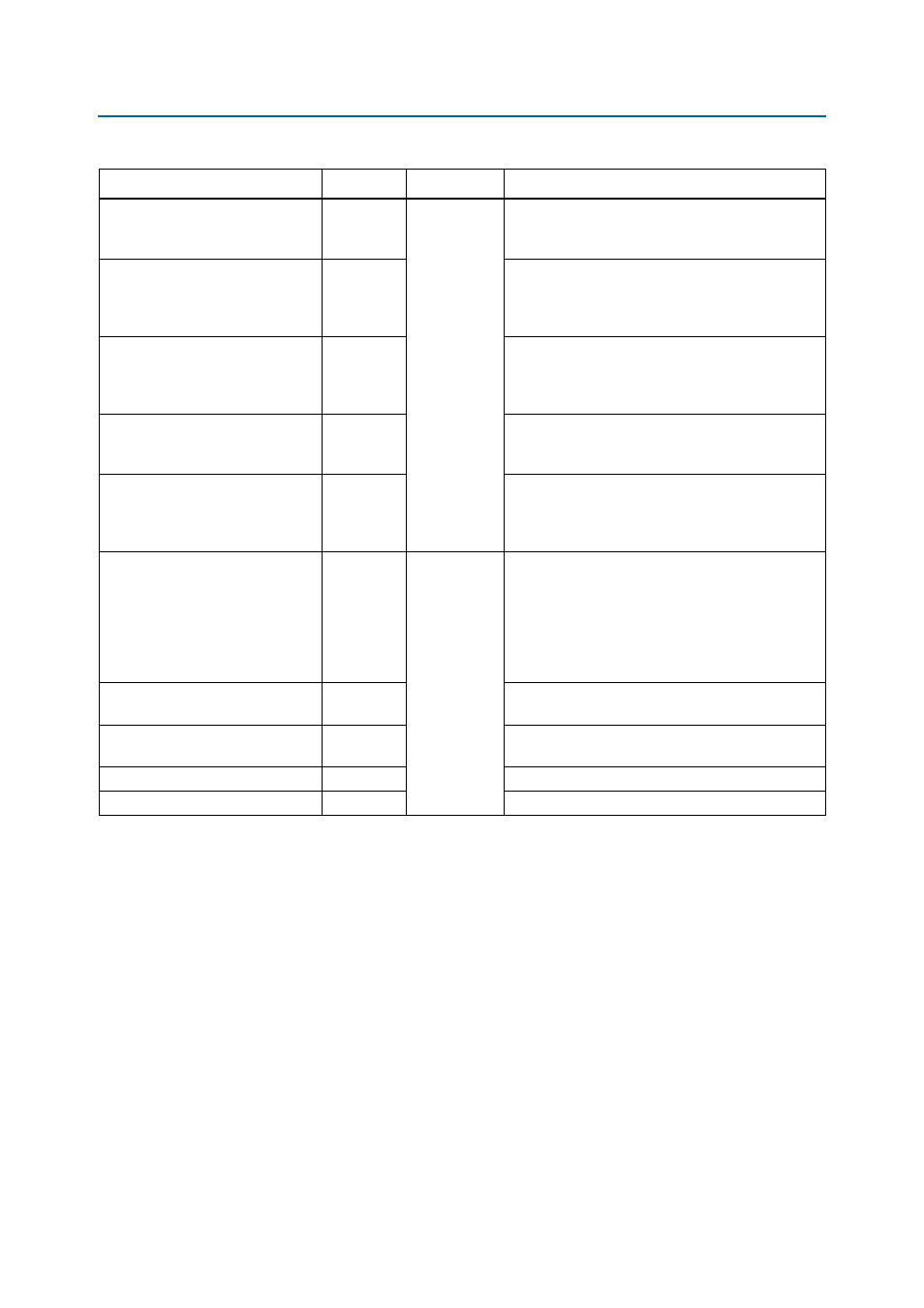

ctl_ts_statedge

Input -

Static

constant

tsclk

Controls the edge of tsclk on which tstat is

sampled (1= positive edge; 0= negative edge). Only

change at reset.

ctl_ts_sync_good_

threshold[3:0]

Input

Number of status frames which must be error free

(err_ts_frm=0 and err_ts_dip2=0) to assert

stat_ts_sync

. Zero is interpreted as one. Only

change at reset.

ctl_ts_sync_bad_

threshold[3:0]

Input

Number of status frames which must be errored

(err_ts_frm=1 and err_ts_dip2=1) to deassert

stat_ts_sync

. Zero is interpreted as one. Only

change at reset.

stat_ts_sync

Output

Indicates status frames are well formed, according to

hysteresis with ctl_ts_synch_good_threshold

and ctl_ts_bad_threshold.

ctl_ts_rsfrm

Input

Forces the status state machine into the disabled

state, beginning at the next frame, at which time

stat_ts_sync

is forced low and

stat_ts_disabled

is asserted.

stat_ts_disabled

Output

tsclk

Indicates that the status state machine is in the

disabled state. Asserted at startup, after the negative

edge of stat_ts_sync, or at a frame boundary if

ctl_ts_rsfrm

is asserted. Deasserted when a

potentially valid framing pattern is detected. A

potentially valid framing word is ‘b11 followed by

anything other than ‘b11.

stat_ts_dip2state

Output

Indicates that the status state machine is in DIP-2

state.

stat_ts_frmstate

Output

Indicates that the status state machine is in framing

state.

stat_ts_exstat_adr[7:0]

Output

Port number for the received status value.

stat_ts_exstat[1:0]

Output

Received status value.

Table 5–7. SPI-4.2 Status Channel Control and Status (Part 2 of 3)

Signal

Direction

Clock Domain

Description