Altera POS-PHY Level 4 IP Core User Manual

Page 29

Chapter 3: Parameter Settings

3–9

Optional Features

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

It is normal during the normal data transfer in SPI-4.2 that dpa_locked signal can

become de-asserted due to some jitter that is still within 0.44 UI of LVDS data. The

DPA has a low pass filter that filters out very high frequency jitter from affecting the

lock signal and phase of rx_clk. If the jitter is detected to be 0.25 UI (two phases out of

8 jump in one direction), dpa_locked is de-asserted and it is still within 0.44 UI.

The DIP-4 error marking determines how the receiver handles DIP-4 errors. The

receiver uses the following three modes to mark received DIP-4 errors:

■

None—no error marking is performed.

■

Optimistic mode—the receiver IP core marks the preceding and succeeding burst

as errored. If these bursts are payload (that is, if a DIP-4 occurs followed by IDLEs),

then only the preceding control word payload is marked as errored. Bursts going

into the Atlantic FIFO buffer are marked with the Atlantic error signal. If a burst is

not an EOP, it is up to the user logic to detect it.

■

Pessimistic mode—the receiver IP core marks all open packets as errored. Packets

going into the Atlantic FIFO buffer are marked with the Atlantic error signal. This

feature increases in resource utilization as the number of ports increases.

End-of-packet-based data available

controls the aN_arxdav signal on the Atlantic

FIFO buffer. Turn on so the aN_arxdav signal is asserted (high) when at least one EOP

is in the buffer, or the fill level is above FIFO threshold low (ctl_ax_ftl). Turn off so

the aN_arxdav signal is asserted (high) only if the fill level of the FIFO buffer is above

the FIFO threshold low value.

The Status source option applies only to variations using the shared buffer with

embedded addressing mode and provides the following two status channel control

options:

■

Buffer Fill Level

—the status for each channel is controlled by the single buffer’s

status. Every calendar time slot contains the result of the almost empty (AE) and

almost full (AF) comparison to the buffer level.

■

User Controlled

—to add extra pins, which allows you to directly control the

transmitted buffer status and allows you to send a status irrespective of the fill

level of the internal FIFO buffers, which avoids the situation where the FIFO

buffer is not emptied quickly enough, and if you still request data, the FIFO buffer

overfills.

Turn on Safe External (User Controlled) Status, to ensure the sent status avoids FIFO

buffer overflow (refer to

Table 3–3

). Turn off Safe External (User Controlled) Status,

to ensure the sent status is always the user status (refer to

Table 3–3

), irrespective of

buffer fill level.

1

If you turn off Safe External (User Controlled) Status, you can overflow the internal

FIFO buffer.

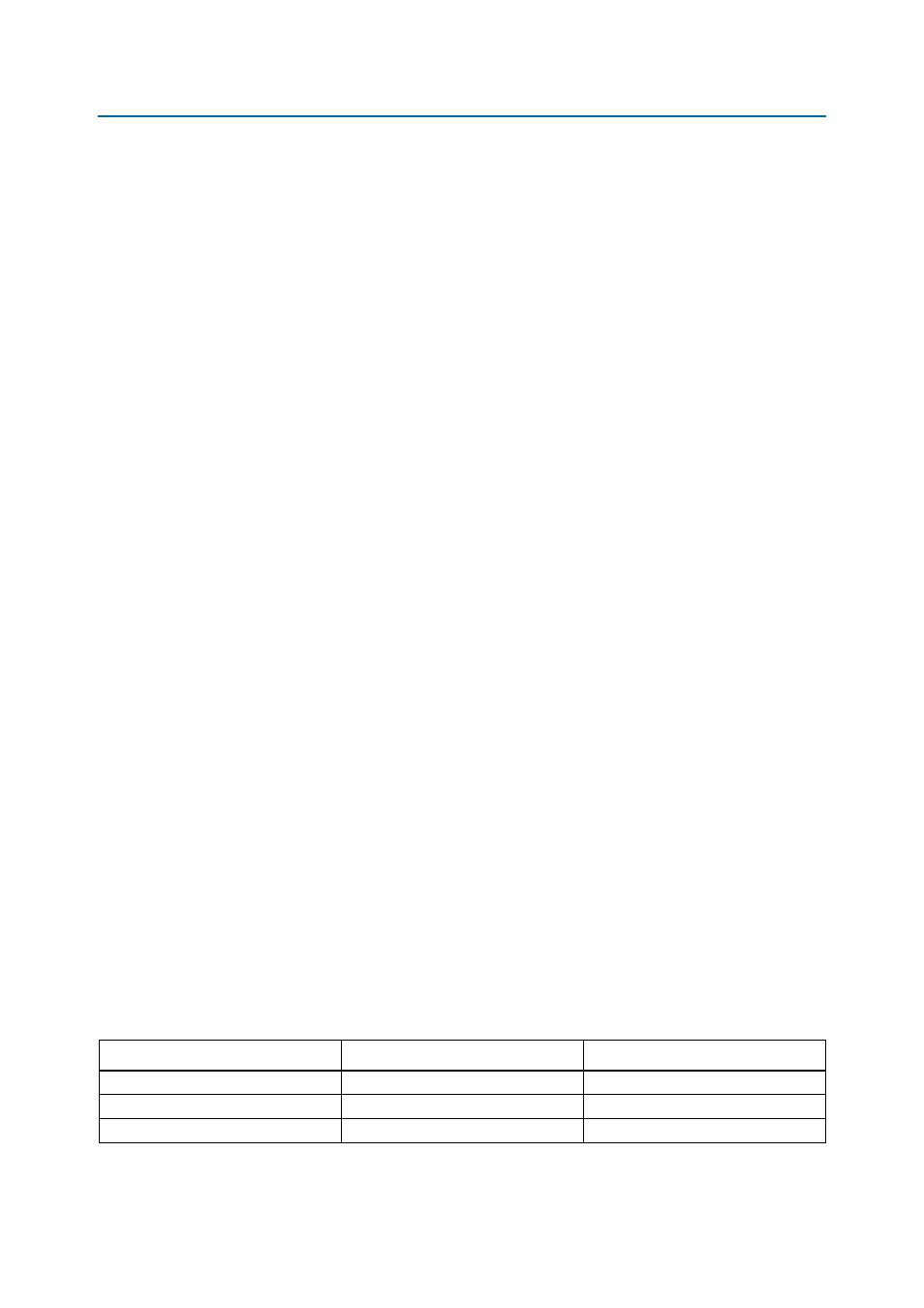

Table 3–3. User-Controlled Option (Part 1 of 2)

User Status Value

FIFO Buffer Status Value

Sent Status Value

Starving

Starving

Starving

Starving

Hungry

Hungry

Starving

Satisfied

Satisfied