Altera POS-PHY Level 4 IP Core User Manual

Page 87

Chapter 5: Functional Description—Transmitter

5–17

Signals

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

.

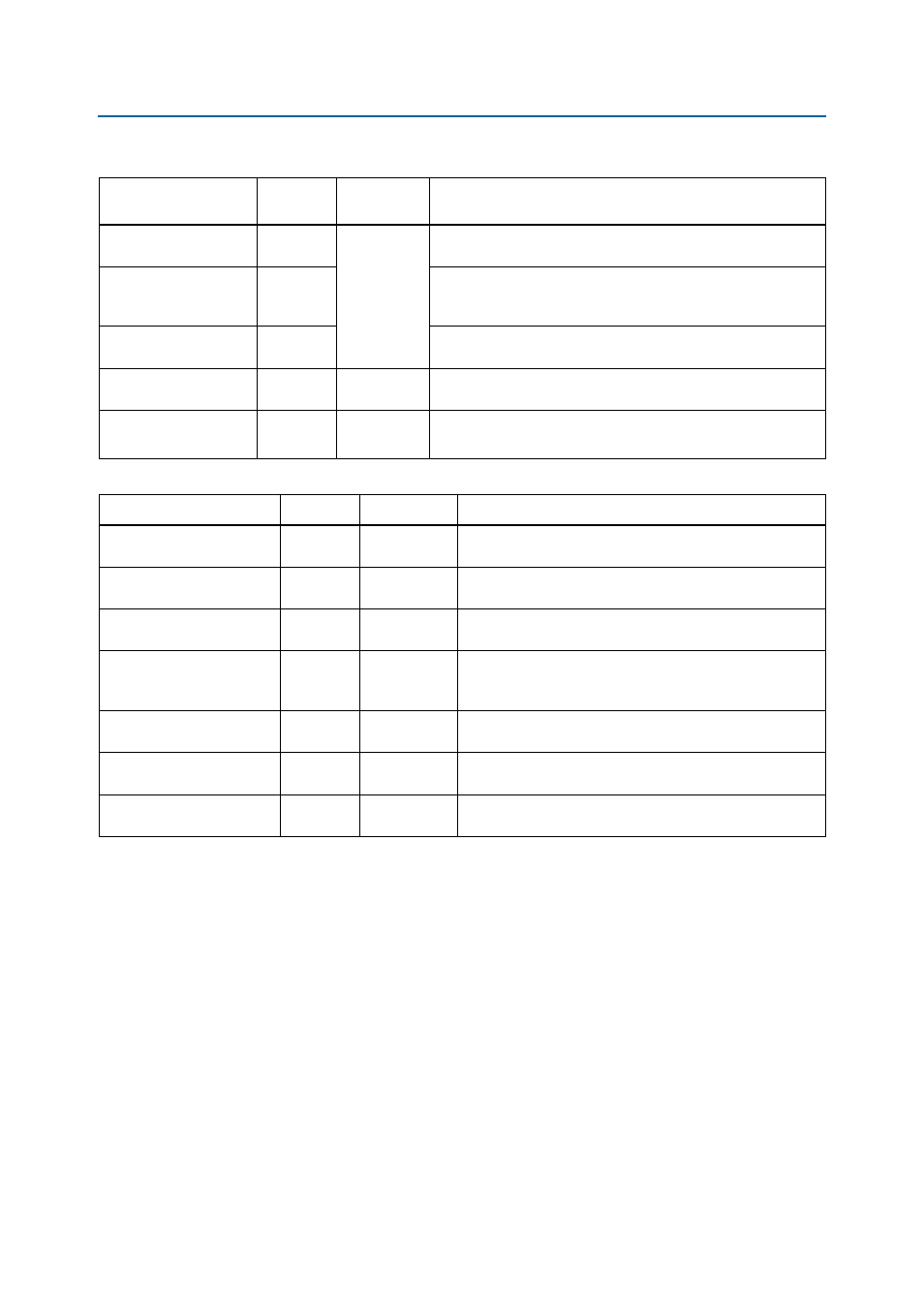

Table 5–3. SPI-4.2 Transmit Interface

Signal

Direction

Clock

Domain

Description

tdclk

Output

tdclk

SPI-4.2 differential transmit clock. Double-data rate clock

synchronous to tctl and tdat.

tctl

Output

SPI-4.2 differential transmit control. When set to logic 1, the word

on tdat is a control word. When set to logic 0, the word on tdat

is a payload word.

tdat[15:0]

Output

SPI-4.2 differential transmit data bus. Bus carries packet/cell

payload or in-band control words.

tsclk

Input

tsclk

SPI-4.2 transmit status clock. All signals infixed by _ts_ are

synchronous to this clock.

tstat[1:0]

Input

tsclk

(either edge)

SPI-4.2 transmit status channel. Indicate the downstream device’s

FIFO buffers fill levels to the upstream device’s scheduler.

Table 5–4. Global

Signal

Direction

Clock Domain

Description

trefclk

Input

trefclk

Transmitter reference clock. Typically route to LVDS PLL.

Signals infixed by _tr_ are synchronous to this clock.

tdint_clk

Output

tdint_clk

Derived from trefclk. Signals infixed by _td_ are

synchronous to this clock.

txsys_clk

Input

txsys_clk

System clock. Signals infixed by _ty_ are synchronous to

this clock.

txreset_n

Input

Asynchronous

Active low asynchronous reset to all internal logic, including

Atlantic FIFO buffers. Refer to

txinfo_aot[12:0]

Output

Static

Fixed output information signal that contains the value for the

current AOT number for the release.

stat_tx_pll_locked

Output

Asynchronous

Locked signal directly from fast PLL in ALTLVDS for full rate

variations. Absent in quarter-rate variations.

ctl_tx_pll_areset

Input

Asynchronous reset signal directly to fast PLL in ALTLVDS for

full-rate variations. Absent in quarter-rate variations.