Altera POS-PHY Level 4 IP Core User Manual

Page 97

Chapter 5: Functional Description—Transmitter

5–27

Latency Information

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

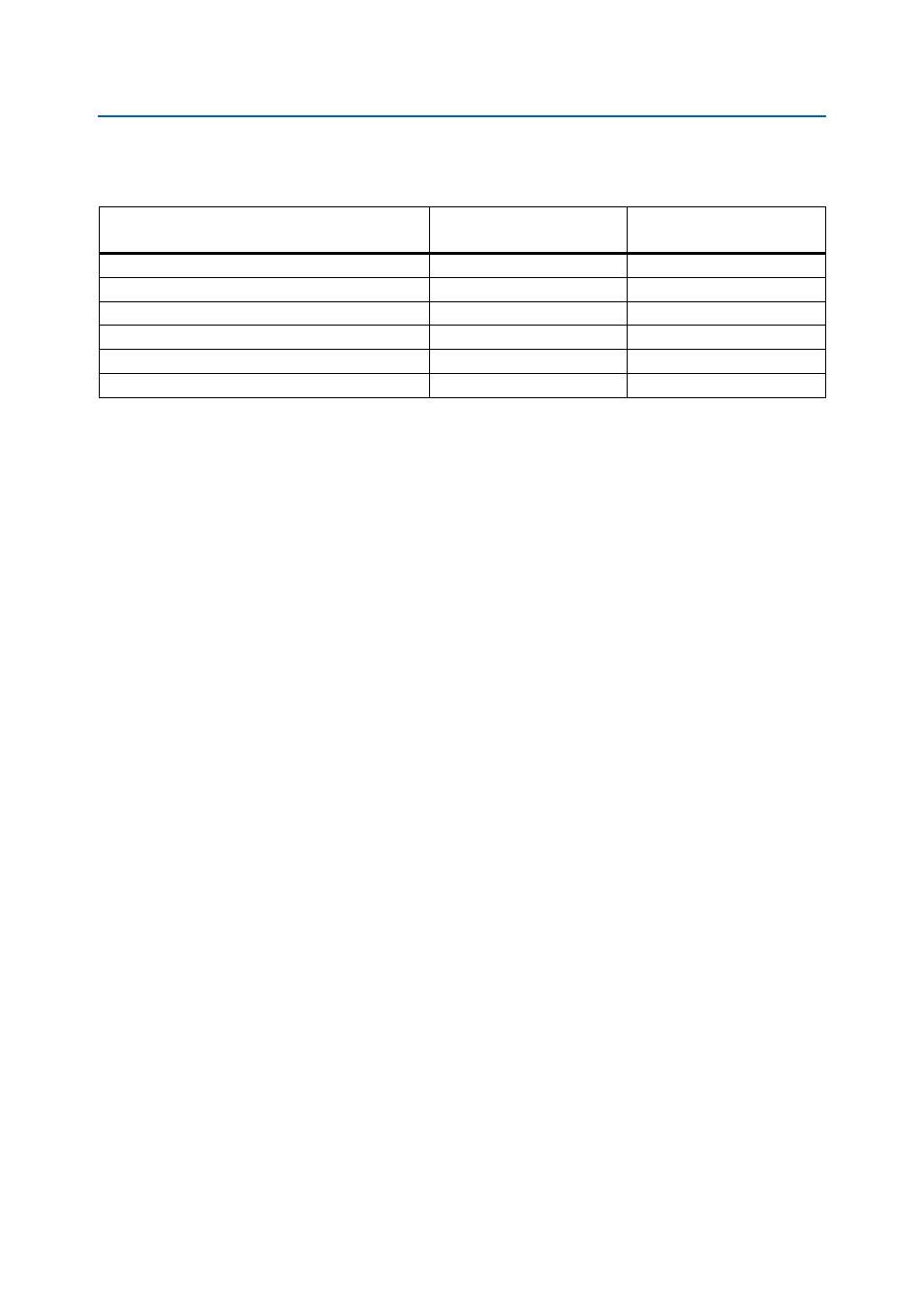

Table 5–11

lists the latency numbers for transmitter variations.

Data latency:

■

The values in

Table 5–11

do not include the latency through the user-side buffers.

■

The external support in the shared buffer with embedded addressing mode adds

8, 4, or 2 bytes for 128-, 64-, and 32-bit data path widths, respectively.

Status latency:

■

The values do not include the time spent waiting for a complete error-free status

message. The resultant value also reflects the status channel mode—either

optimistic or pessimistic.

■

Turning on Lite Transmitter adds up to 32 bytes for 128-bit data path widths, or

up to 16 bytes for 64-bit data path widths.

Table 5–11. Transmitter Latency

IP core

Data Latency

(Bytes on SPI-4.2 Interface)

Status Receive Latency

(Bytes on SPI-4.2 Interface)

128-bit shared buffer with embedded addressing

160

256

128-bit individual buffers

160

256

64-bit shared buffer with embedded addressing

128

256

64-bit individual buffers

128

256

32-bit shared buffer with embedded addressing

64

256

32-bit individual buffers

64

256