Interfaces & protocols, Spi-4.2 interface, Atlantic interface – Altera POS-PHY Level 4 IP Core User Manual

Page 6: Avalon-mm interface

1–4

Chapter 1: About This IP Core

General Description

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

Interfaces & Protocols

The following three interfaces support the POS-PHY Level 4 IP core:

■

SPI-4.2 interface

■

Atlantic

™

interface

■

Avalon

®

Memory-Mapped (Avalon-MM) interface.

You can use multiple Atlantic interfaces, but the SPI-4.2 interface only supports a

single transmitter and a single receiver.

SPI-4.2 Interface

The SPI-4.2 interface is an external interface protocol developed by the Optical

Internetworking Forum (OIF). The SPI-4.2 interface features a high-speed data

portion and a FIFO buffer status portion. The high-speed portion comprises a 16-bit

data bus, a 1-bit control line, and a double data rate (DDR) clock. The FIFO buffer

status portion comprises a 2-bit status channel and a clock.

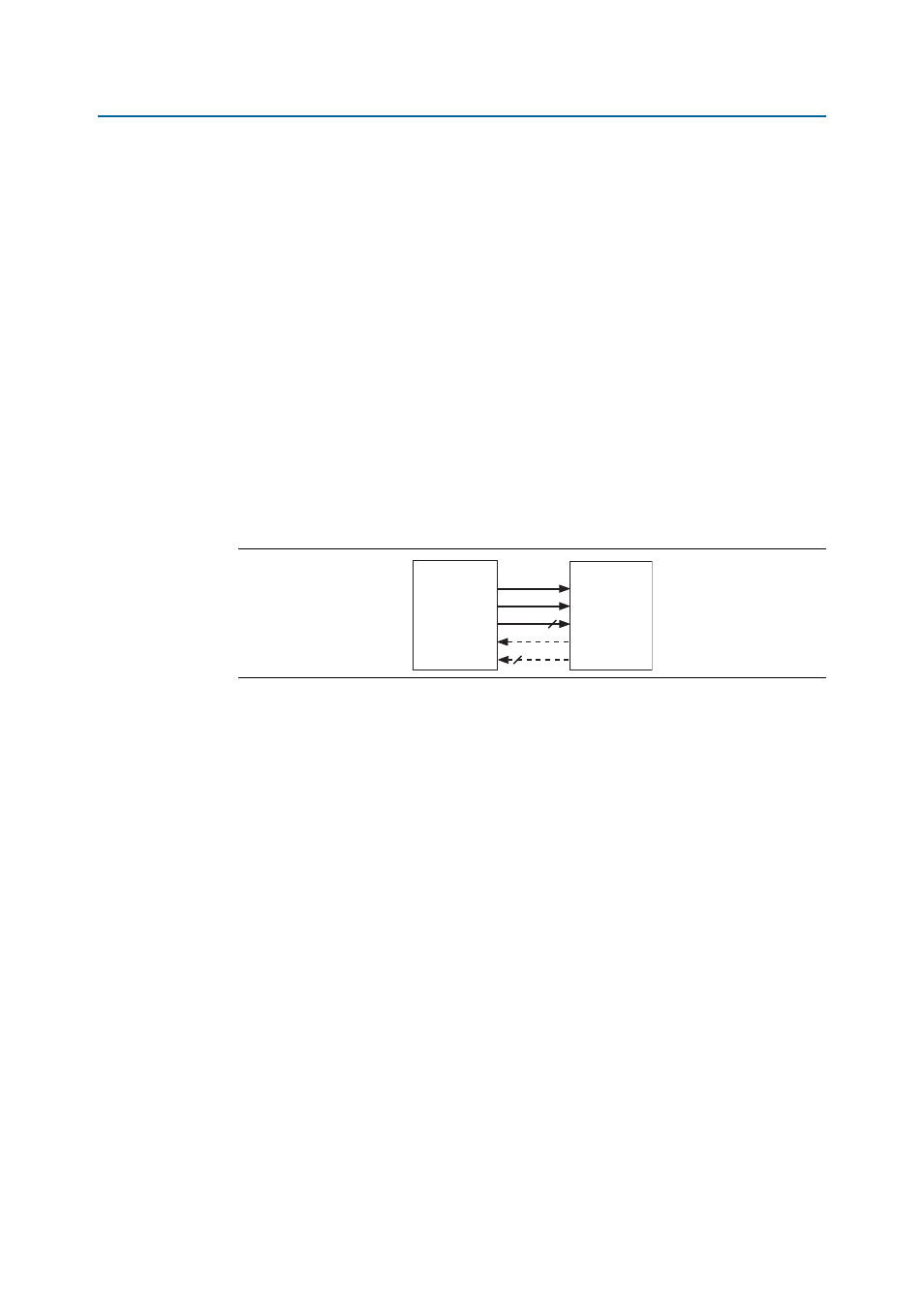

Figure 1–3

shows a full-duplex SPI-4.2 configuration.

f

For further information on this interface, refer to the System Packet Interface Level 4

(SPI-4) Phase 2 Revision 1: OC-192 System Interface for Physical and Link Layer Devices,

avai

.

Atlantic Interface

The Atlantic interface is an Altera-developed synchronous protocol supporting both

packets and cells. The POS-PHY Level 4 IP core is an Atlantic interface slave that

transfers packets to or from the user-side logic. The Atlantic interface provides a

connection between the FIFO buffer and user logic.

f

For further information on this interface, refer to the

Avalon-MM Interface

The Altera Avalon-MM interface is a simple bus architecture that connects on-chip

processors (or external processor interfaces) and peripherals. The Avalon-MM

interface specifies the port connections between master and slave components, and

specifies the timing by which these components communicate.

All Avalon-MM signals are synchronized to the Avalon-MM clock (rav_clk/tav_clk).

This synchronization simplifies the relevant timing behavior of the Avalon-MM

interface and facilitates integration with high-speed peripherals.

Figure 1–3. SPI-4.2 Top-Level View

Transmitter

Source

Receiver

Sink

tsclk

tstat[1:0]

tdclk

tctl

tdat[15:0]

rsclk

rstat[1:0]

rdclk

rctl

rdat[15:0]