R to, And to – Altera CPRI IP Core User Manual

Page 102

6–4

Chapter 6: Signals

MAP Interface Signals

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

lists the MAP transmitter interface signals.

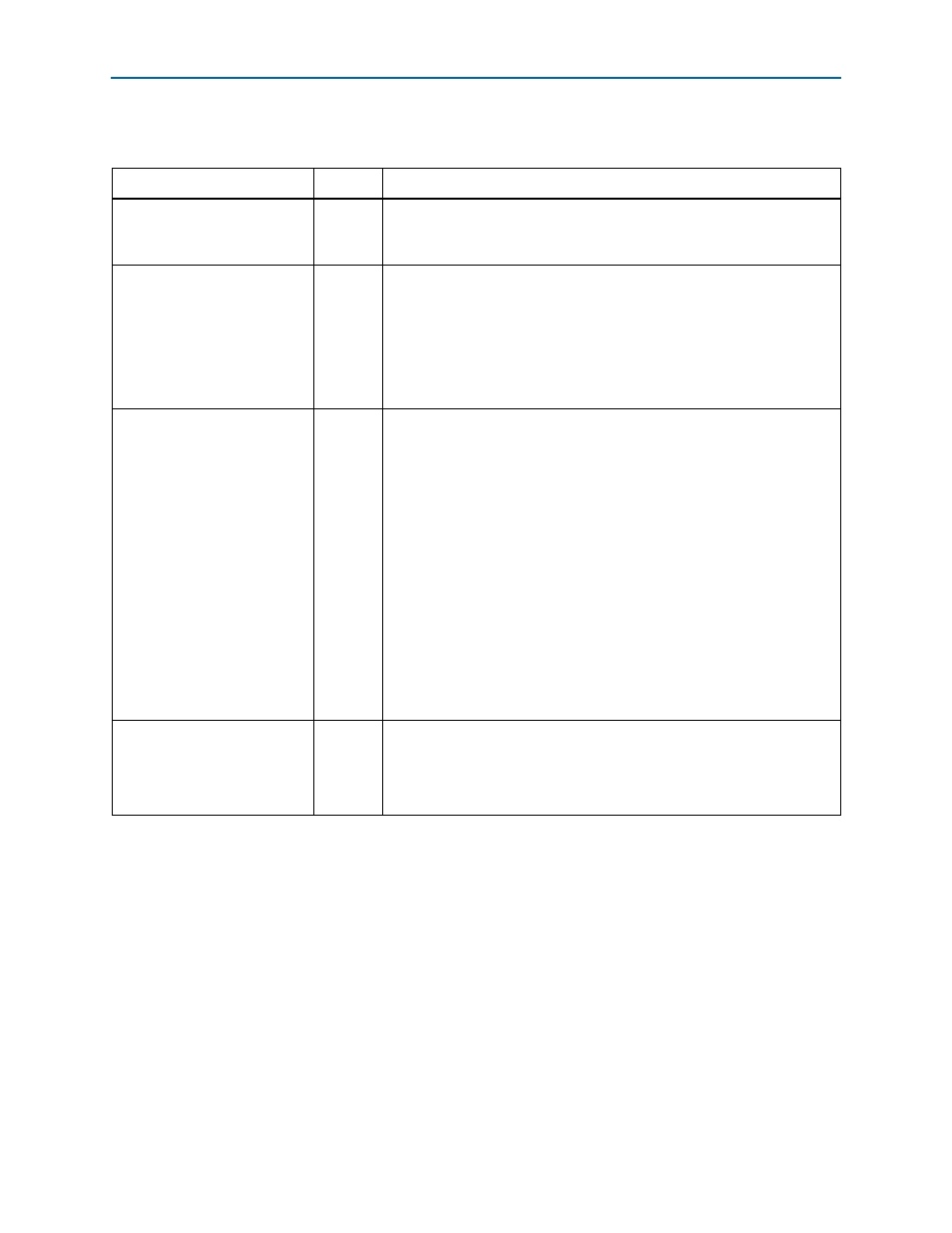

Table 6–2. MAP Transmitter Interface Signals (Part 1 of 2)

Signal

Direction

Description

map{23…0}_tx_clk

Input

Clock signal for each antenna-carrier interface.

These clocks are not supported in the internally-clocked mode. In the

interally-clocked mode,

cpri_clkout

clocks the antenna-carrier interfaces.

map{23…0}_tx_reset

Input

Reset signal for each antenna-carrier interface in synchronous buffer mode

and in FIFO mode. This reset is associated with the

mapN_tx_clk

clock.

These signals are not supported in the internally-clocked mode.

mapN_tx_reset

can be asserted asynchronously, but must stay asserted at

least one cycle of the associated clock, and must be deasserted

synchronously with that clock. Refer to

for a circuit

that shows how to enforce synchronous deassertion of a reset signal.

map{23…0}_tx_valid

Input

Write-valid signal for each antenna-carrier interface. This signal qualifies all

the other Avalon-ST input signals of the MAP transmitter interface. On every

rising edge of the clock at which

mapN_tx_valid

is high, data is sampled by

the CPRI IP core.

In FIFO mode, the application can assert

mapN_tx_valid

in any

mapN_tx_clk

cycle immediately following a

mapN_tx_clk

cycle in which

the CPRI IP core asserts the

mapN_tx_ready

signal for the corresponding

antenna-carrier interface.

In synchronous buffer mode, the application must assert the

mapN_tx_valid

signal at the same time as or immediately after it asserts

the

mapN_tx_resync

resynchronization signal. However, Altera

recommends that the application assert these two signals simultaneously.

Refer to

“MAP Transmitter in Synchronous Buffer Mode” on page 4–27

In the internally-clocked mode, the application must wait at least one

cpri_clkout

cycle after the IP core asserts

mapN_tx_ready

before

asserting the

mapN_tx_valid

signal;

READY_LATENCY

is 1.

map{23…0}_tx_data[31:0]

Input

32-bit write data from each antenna-carrier interface. Data is valid starting

one

mapN_tx_clk

clock cycle (

cpri_clkout

clock cycle in the

internally-clocked mode) after the write-valid bit is asserted. Bits [15:0] are

the I component of the IQ sample. Bits [31:16] are the Q component of the IQ

sample.