Altera CPRI IP Core User Manual

Page 40

4–8

Chapter 4: Functional Description

Clocking Structure

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

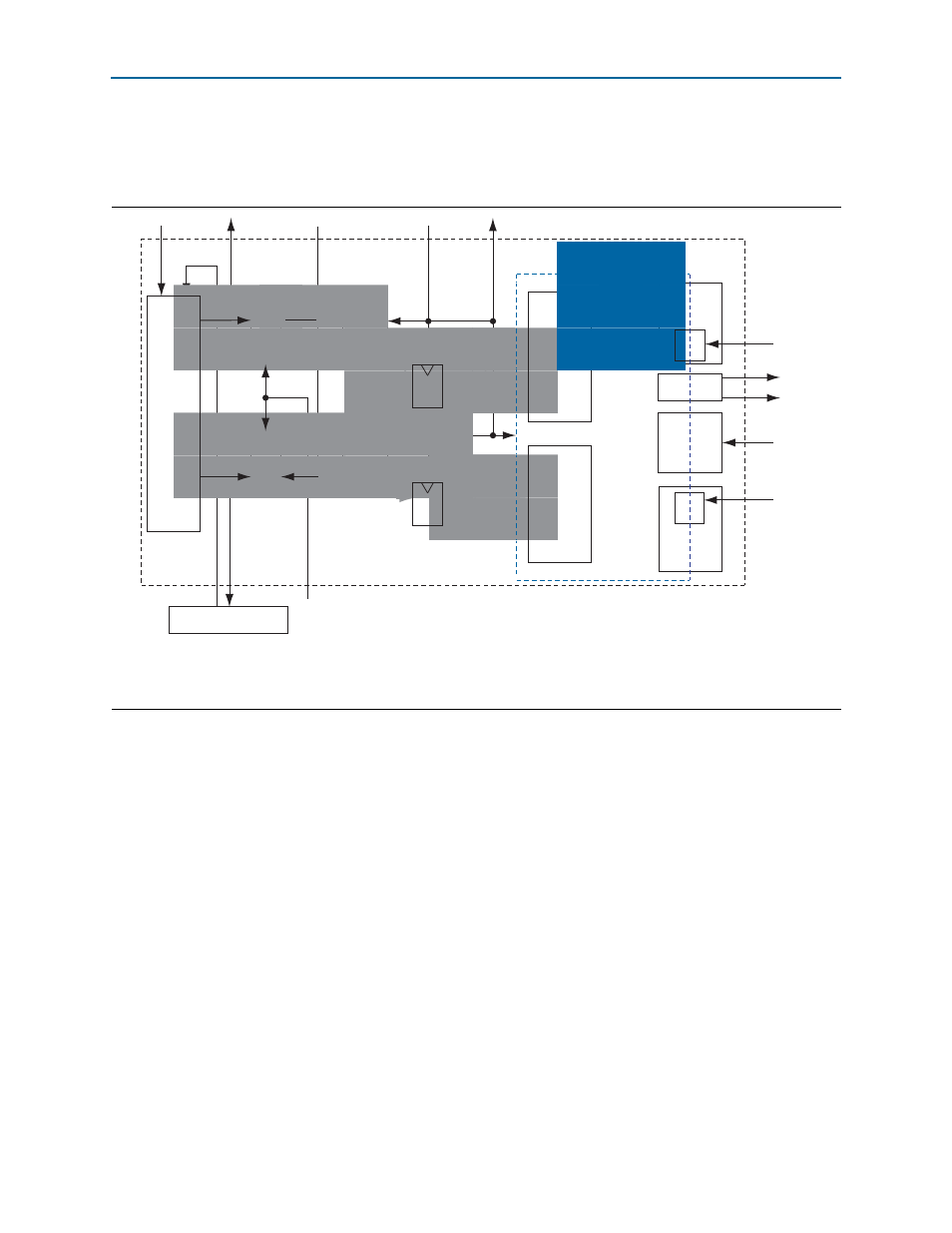

shows the clocking scheme for a CPRI IP core that targets an Arria V GT

device and is configured with a CPRI line rate of 9830.4 Mbps, configured or

programmed as an RE slave.

Figure 4–4. CPRI IP Core Slave Clocking in Arria V GT 9.8 Gbps Variations

Notes to

(1) In slave clocking mode, the

usr_clk

and

usr_pma_clk

input clocks must be driven by a common source from the cleanup PLL. For additional

constraints these clocks require, refer to

CPRI MegaCore Function

clk_ex_delay

pll_clkout

cpri_clkout

usr_clk

(245.76 MHz)

usr_pma_clk

(122.88 MHz)

gxb_refclk

gxb_pll_inclk

tx_clkout

TX

Buffer

RX

Buffer

122.88 MHz

122.88 MHz

Soft

PCS

Soft

PCS

tx_clkout

rx_clkout

Transceiver

Native PHY

IP Core

CPRI TX

MII Interface

CPU

Interface

CPRI RX

FIFO

Buffer

cpu_clk

mapN_tx_clk

FIFO

Buffer

mapN_rx_clk

CPRI Rx

MAP

Interface

CPRI Tx

MAP

Interface

cpri_mii_txclk

cpri_mii_rxclk

Clean-Up PLL