Test sequence, Test sequence –3 – Altera CPRI IP Core User Manual

Page 151

Chapter 8: CPRI IP Core Demonstration Testbench

8–3

Test Sequence

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

Test Sequence

The non-autorate negotiation testbench starts by resetting the CPRI IP core.

Table 8–2

lists the frequencies of the clock inputs to the CPRI IP core.

After coming out of the reset state, the CPRI IP core performs the frame

synchronization process to establish frame synchronization.

The testbench then performs the following actions:

■

Sends a predetermined data sequence to the AUX interface, and checks that the

data appears on the outgoing AUX interface after loopback through the CPRI link.

■

If the IP core includes at least one antenna-carrier interface, the testbench

generates a sequence of 32-bit words and sends the data sequence to each

antenna-carrier interface that is enabled.

If at least one antenna-carrier interface is enabled, the testbench then checks that

the data sent to the mapN interfaces appears on the outgoing antenna-carrier

interface data channels, after loopback through the CPRI link.

■

If the IP core includes the MI interface, the testbench sends a predetermined data

sequence to the MII, and checks that the data appears as expected on the outgoing

MII after loopback through the CPRI link.

This test also checks the MII handling of the input error indication signal. The

signal is asserted during parts of the incoming data sequence, and the expected

output data reflects the correct handling of data in this case.

■

If the IP core includes an HDLC block, the testbench programs a predetermined

sequence of data transactions for HDLC communication through the CPU

interface, and checks that the responses appear as expected in the CPRI IP core

HDLC registers after data transaction loopback through the CPRI link.

The testbench performs self-checking and outputs the pass/fail results to your

simulator session or transcript. In addition, the testbench includes simulator files that

allow you to observe the signals in and out of the CPU interface, AUX interface,

antenna-carrier interfaces, and MII if relevant.

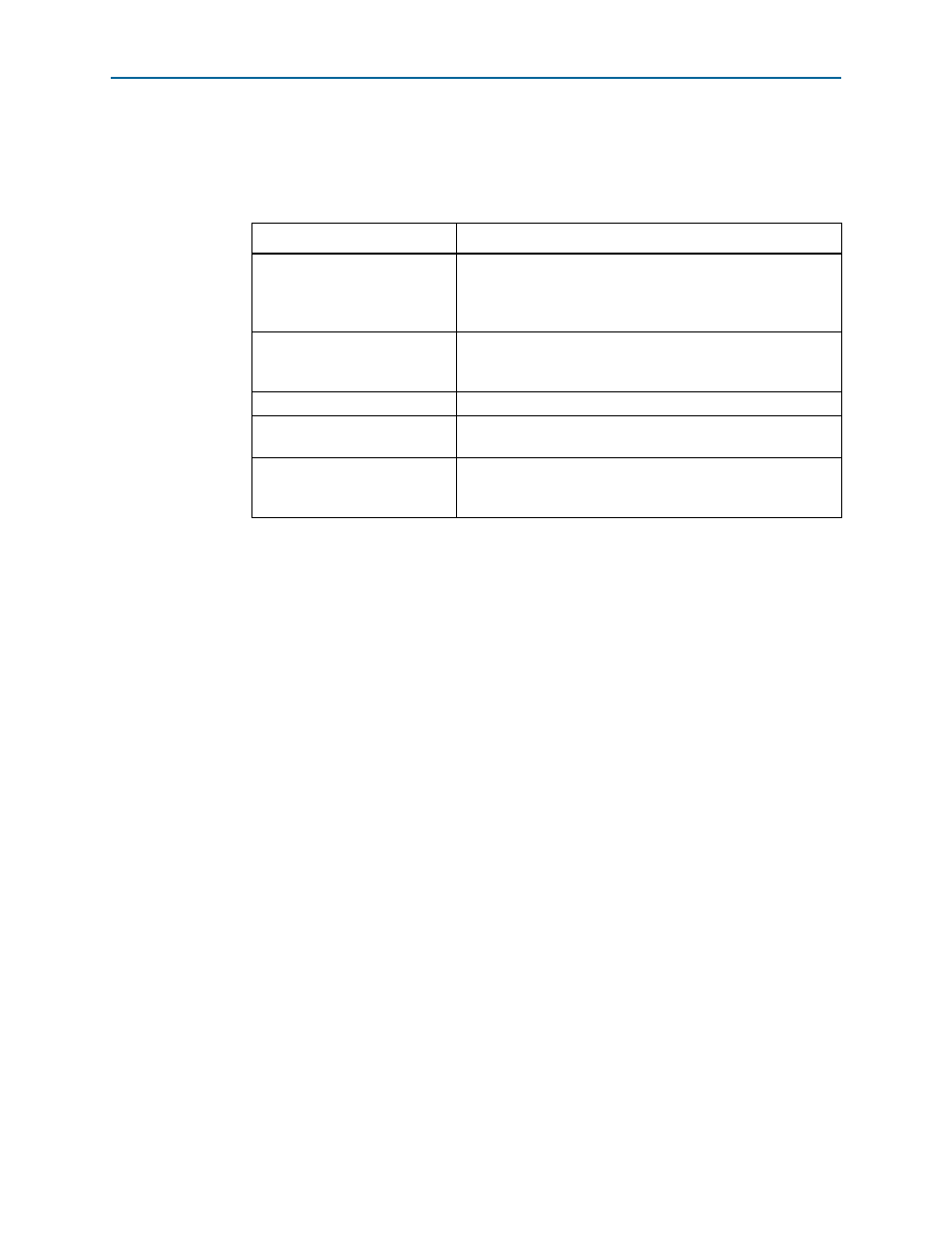

Table 8–2. Clock Frequencies for CPRI IP Core Under Test

Clock

Frequency (MHz)

gxb_refclk

The testbench sets the

gxb_refclk

frequency according to the

Transceiver reference clock frequency parameter value in CPRI

IP core variations that target a 28-nm device, and according to

in all other variations.

cpu_clk

the testbench sets the

cpu_clk

frequency to match the

frequency of the output clock cpri_clkout. Refer to

clk_ex_delay

30.96

mapN_tx_clk

mapN_rx_clk

3.84

reconfig_clk

The testbench sets the

reconfig_clk

frequency to 100 MHz in

CPRI IP core variations that target a 28-nm device, and to 50

MHz in all other variations.