Cpri protocol interface registers, Cpri protocol interface registers –2 – Altera CPRI IP Core User Manual

Page 118

7–2

Chapter 7: Software Interface

CPRI Protocol Interface Registers

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

CPRI Protocol Interface Registers

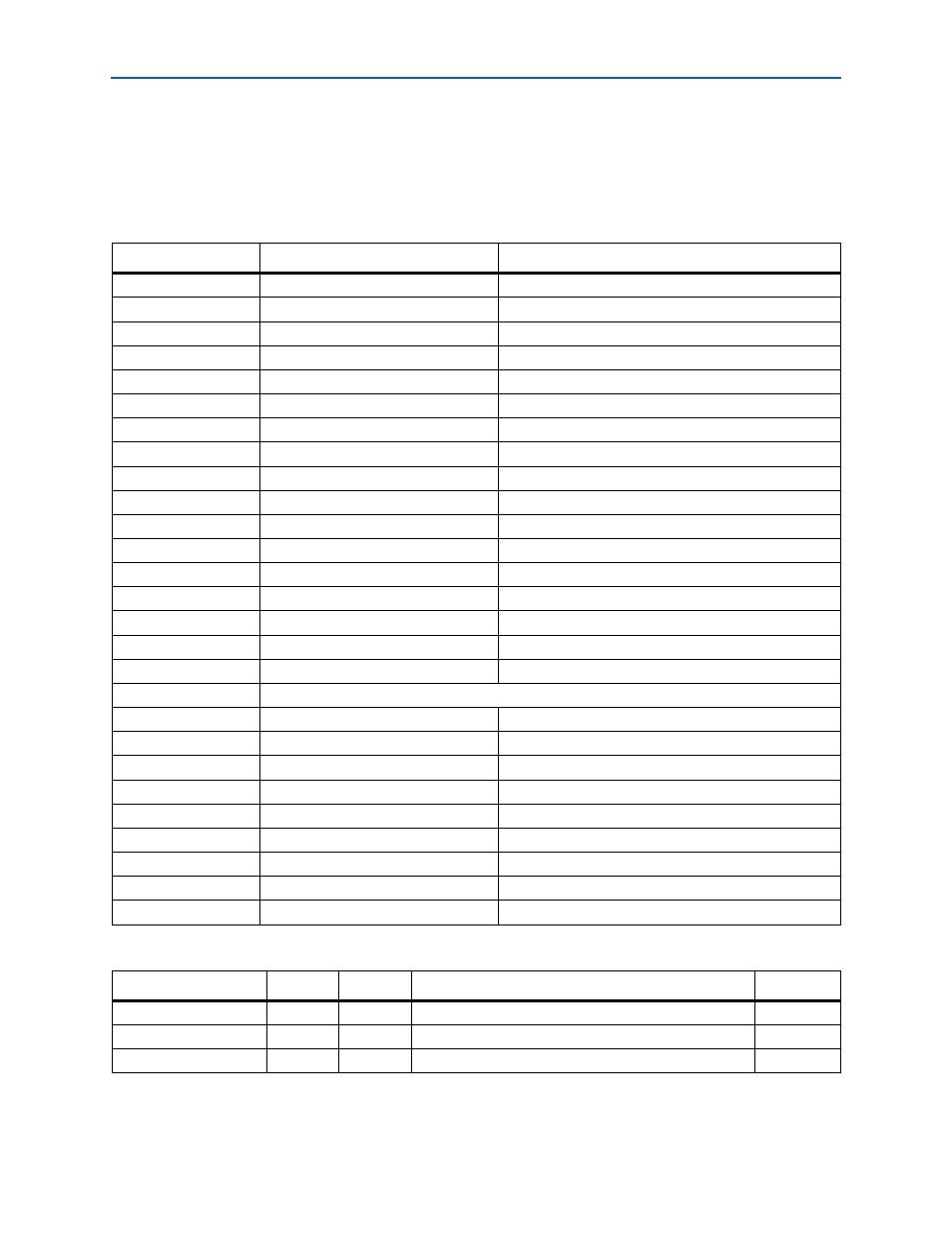

This section lists the CPRI protocol interface registers.

map for the CPRI protocol interface registers.

through

describe

the CPRI protocol interface registers in the CPRI IP core.

Table 7–3. CPRI Protocol Interface Registers Memory Map

Address

Name

Expanded Name

0x0

CPRI_INTR

Interrupt Control and Status

0x4

CPRI_STATUS

CPRI Status

0x8

CPRI_CONFIG

CPRI Configuration

0xC

CPRI_CTRL_INDEX

CPRI Control Word Index

0x10

CPRI_RX_CTRL

CPRI Received Control Word

0x14

CPRI_TX_CTRL

CPRI Transmit Control Word

0x18

CPRI_LCV

CPRI Line Code Violation Counter

0x1C

CPRI_RX_BFN

CPRI Recovered Radio Frame Counter

0x20

CPRI_HW_RESET

Hardware Reset From Control Word

0x24

CPRI_PHY_LOOP

Physical Layer Loopback Control

0x28

CPRI_CM_CONFIG

CPRI Control and Management Configuration

0x2C

CPRI_CM_STATUS

CPRI Control and Management Status

0x30

CPRI_RX_DELAY_CONTROL

Receiver Delay Control

0x34

CPRI_RX_DELAY

Receiver Delay

0x38

CPRI_ROUND_DELAY

Round Trip Delay

0x3C

CPRI_EX_DELAY_CONFIG

Extended Delay Measurement Configuration

0x40

CPRI_EX_DELAY_STATUS

Extended Delay Measurement Status

0x44

Reserved

0x48

AUTO_RATE_CONFIG

Autorate Negotiation

0x4C

CPRI_INTR_PEND

Pending Interrupt Status

0x50

CPRI_N_LCV

LCV Threshold

0x54

CPRI_T_LCV

LCV Test Period

0x58

CPRI_TX_PROT_VER

Tx Protocol Version

0x5C

CPRI_TX_SCR_SEED

Tx Scrambler Seed

0x60

CPRI_RX_SCR_SEED

Rx Scrambler Support

0x64

CPRI_TX_BITSLIP

Tx Bitslip

0x68

CPRI_AUTO_CAL

Autocalibration

Table 7–4. CPRI_INTR—Interrupt Control and Status—Offset: 0x0 (Part 1 of 2)

Field Bits

Access

Function

Default

RSRV

[31:6]

UR0

Reserved.

31’h0

intr_los_lcv_en

[5]

RW

los_lcv interrupt enable.

1’h0

RSRV

[4:2]

UR0

Reserved.

3’h0