Altera CPRI IP Core User Manual

Page 140

7–24

Chapter 7: Software Interface

Ethernet Registers

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

rx_eop

[1]

RO

Indicates that the next ready data word contains the end-of-packet

byte.

1’h0

rx_ready

[0]

RO

Indicates that at least one 32-bit word of Ethernet data is available in

the Ethernet Rx buffer and ready to be read.

1’h0

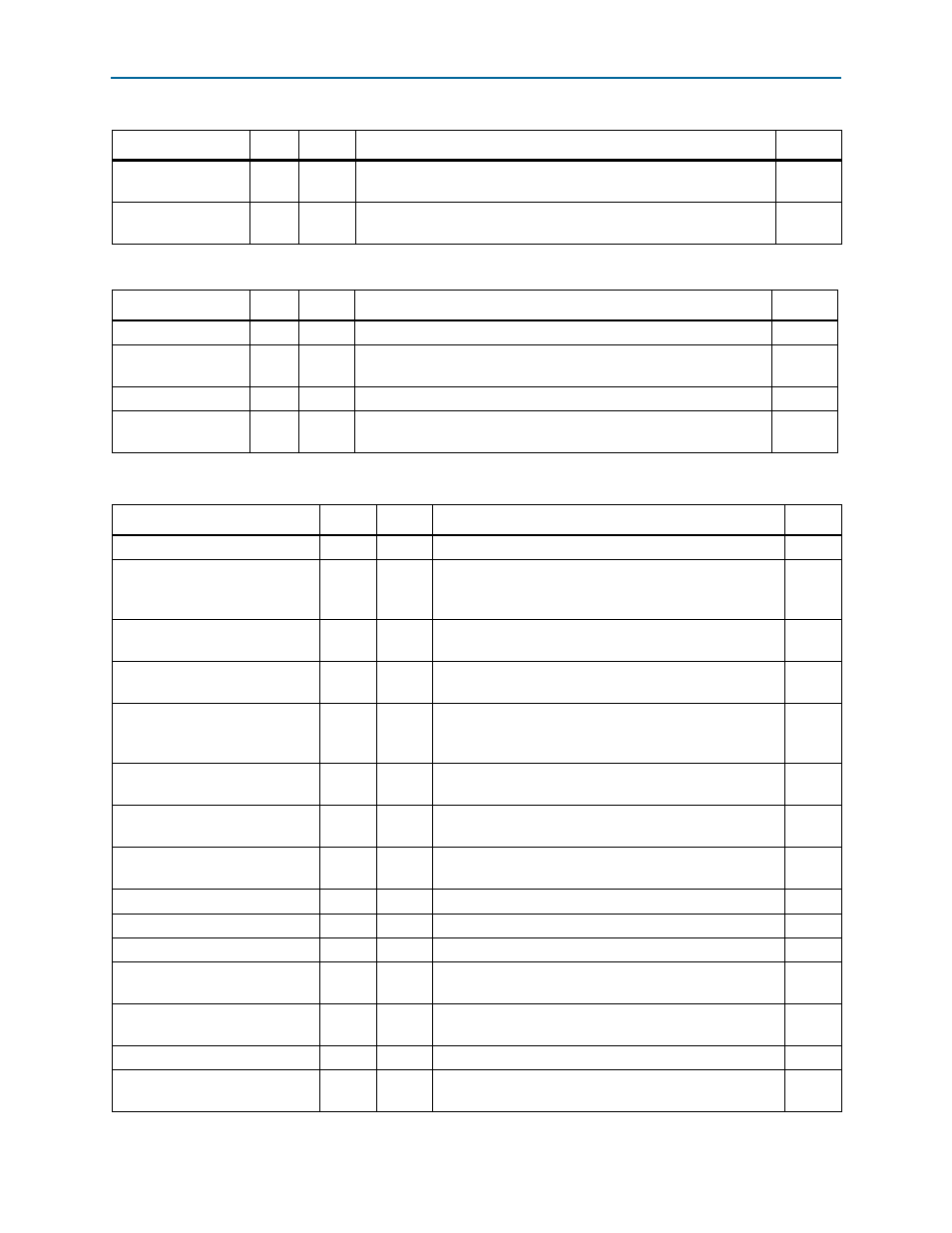

Table 7–51. ETH_RX_STATUS—Ethernet Receiver Module Status—Offset: 0x200 (Part 2 of 2)

Field

Bits

Access

Function

Default

Table 7–52. ETH_TX_STATUS—Ethernet Transmitter Module Status—Offset: 0x204

Field

Bits

Access

Function

Default

RSRV

[31:3] UR0

Reserved.

29'h0

tx_ready_block

[2]

RO

Indicates that the Ethernet Tx module is ready to receive an 8-word

block of data.

1’h0

tx_abort

[1]

RO

Indicates the current Ethernet Tx packet is aborted.

1’h0

tx_ready

[0]

RO

Indicates that the Ethernet Tx module is ready to receive at least one

32-bit word of data.

1’h0

Table 7–53. ETH_CONFIG_1—Ethernet Feature Configuration 1—Offset: 0x208 (Part 1 of 2)

Field

Bits

Access

Function

Default

RSRV

[31:20] UR0

Reserved.

11'h0

intr_tx_ready_block_en

[19]

RW

Indicates an interrupt is generated when

tx_ready_block

is asserted, if

intr_en

and

intr_tx_en

are asserted.

1’h0

intr_tx_abort_en

[18]

RW

Indicates an interrupt is generated when

tx_abort

is

asserted, if

intr_en

and

intr_tx_en

are asserted.

1’h0

intr_tx_ready_en

[17]

RW

Indicates an interrupt is generated when

tx_ready

is

asserted, if

intr_en

and

intr_tx_en

are asserted.

1’h0

intr_rx_ready_block_en

[16]

RW

Indicates an interrupt is generated when

rx_ready_block

is asserted, if

intr_en

and

intr_rx_en

are asserted.

1’h0

intr_rx_ready_end_en

[15]

RW

Indicates an interrupt is generated when

rx_ready_end

is

asserted, if

intr_en

and

intr_rx_en

are asserted.

1’h0

intr_rx_abort_en

[14]

RW

Indicates an interrupt is generated when

rx_abort

is

asserted, if

intr_en

and

intr_rx_en

are asserted.

1’h0

intr_rx_ready_en

[13]

RW

Indicates an interrupt is generated when

rx_ready

is

asserted, if

intr_en

and

intr_rx_en

are asserted.

1’h0

intr_tx_en

[12]

RW

Ethernet Tx interrupt enable.

1’h0

intr_rx_en

[11]

RW

Ethernet Rx interrupt enable.

1’h0

intr_en

[10]

RW

Ethernet global interrupt enable.

1’h0

rx_long_frame_en

[9]

RW

Enable reception of Rx Ethernet frames longer than 1536

bytes.

1’h0

rx_preamble_abort_en

[8]

RW

Indicates that Rx frames with an illegal preamble nibble

before the SFD are discarded.

1’h0

broadcast_en

[7]

RW

Enable reception of Ethernet broadcast packets.

1’h0

multicast_flt_en

[6]

RW

Enable reception of multicast Ethernet packets allowed by

the hash function.

1’h0