Single-hop delay measurement, Rx path delay, Most cpri ip core variations – Altera CPRI IP Core User Manual

Page 181

Appendix E: Delay Measurement and Calibration

E–3

Single-Hop Delay Measurement

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

1

sections do not discuss the delays through

the AxC blocks, because the round-trip delay calculations and the multihop

configuration delay calculations do not take the AxC blocks into account. For

purposes of these calculations, the relevant SAP is the AUX interface. For information

about the delays through the AxC blocks, refer to

“MAP Transmitter Interface” on page 4–24

Single-Hop Delay Measurement

The following sections describe the RX and TX path delays for single-hop variations

and provide examples.

Rx Path Delay

The Rx path delay is the cumulative delay from the arrival of the first bit of a 10 ms

radio frame on the CPRI Rx interface to the start of transmission of the radio frame on

the AUX interface. The following sections describe the delay for the following

variations:

■

■

Most CPRI IP Core Variations

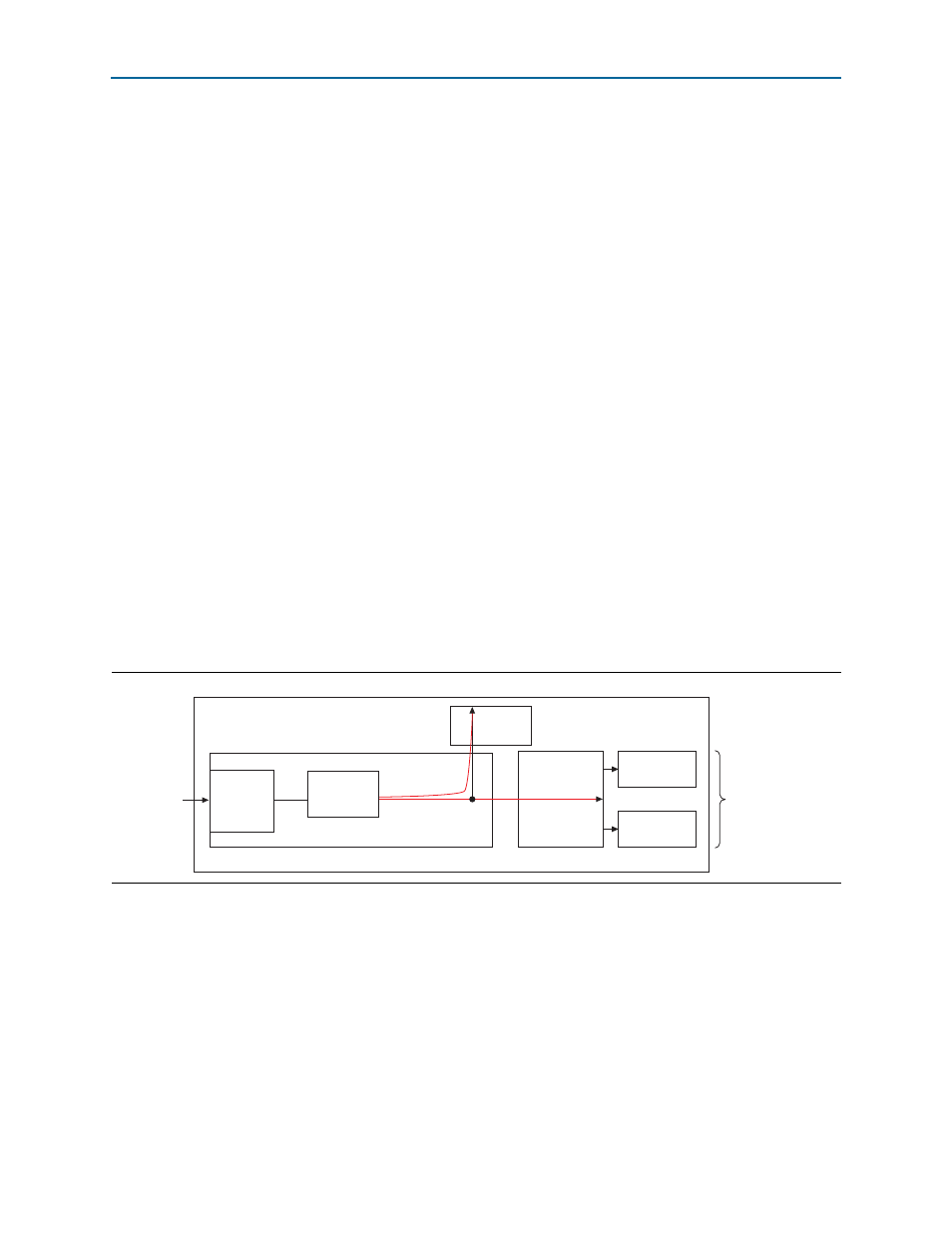

Figure E–3

shows the Rx path delay components in all CPRI IP core variations except

those that target an Arria V GT device and are configured with the CPRI line rate of

9.8 Gbps. The figure shows the relation between the two Rx paths.

Figure E–3. Rx Path Delay to AUX Output and Through MAP Interface Block in Most CPRI IP Core Variations

AxC IF 0

AxC IF n

...

AUX Interface

Data Channels

Rx

Transceiver

Receiver

rx_datain

Physical Layer

CPRI MAP

Interface Module

AUX

Module

Rx Elastic

Buffer

(1a)

(1c)

(1b)

(2)

(2)

(1d) (1e)