Altera CPRI IP Core User Manual

Page 209

Appendix F: Integrating the CPRI IP Core Timing Constraints in the Full Design

F–3

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

After you complete your design, you must modify the clock names in the .sdc file to

the full-design clock names, taking into account both the CPRI IP core instance name

in the full design, and the design hierarchy. After you make the required

modifications, the example .sdc file contains the following substitute timing

constraints:

#ALTGX Transceiver Reference Clock

create_clock -name

cpri_ref_clk

-period 6.510 -waveform {0.000 3.255} [get_ports

cpri_ref_clk

]

#Clock from Clean-Up PLL (RE slave only)

create_clock -name

cleaned_clkin

-period 6.510 -waveform {0.000 3.255} [get_ports

cleaned_clkin

]

#50MHz Clock to Drive Calibration Block Clock, CPU Clock, and Reconfig Clock

create_clock -name clkin_50mhz -period 20.000 -waveform {0.000 10.000} [get_ports

clkin_50mhz]

derive_pll_clocks

derive_clock_uncertainty

set_false_path -from * -to

*cpri_0_inst

*sync

set_false_path -from * -to

*cpri_0_inst

*sync[*]

set_false_path -from * -to

*cpri_0_inst

*sync1

set_false_path -from * -to

*cpri_0_inst

*sync1[*]

set_false_path -from * -to

*cpri_0_inst

*s0

set_false_path -from * -to

*cpri_0_inst

*s0[*]

create_generated_clock -name txclk_div2 -source [get_pins -compatibility_mode

*cpri_0_inst

*transmit_pcs0|clkout] -divide_by 2 [get_registers

*cpri_0_inst

*txclk_div2]

derive_clock_uncertainty

set_clock_groups -exclusive -group txclk_div2 -group

*cpri_0_inst

*receive_pcs0|clkout

set_clock_groups -exclusive -group

*cpri_0_inst

*transmit_pcs0|clkout -group

*cpri_0_inst

*receive_pcs0|clkout

set_clock_groups -asynchronous -group

clkin_50mhz

-group txclk_div2

set_clock_groups -asynchronous -group

pll1|clk[0]

-group txclk_div2

set_clock_groups -asynchronous -group

pll2|clk[0]

-group {txclk_div2

*cpri_0_inst

*transmit_pcs0|clkout

*cpri_0_inst

*receive_pcs0|clkout}

The example illustrates the following guidelines you must follow when finalizing the

.sdc

file for your design:

■

The CPRI IP core clock ports are not in one-to-one correspondence with the full

design input clock ports. You must use the correspondence between the

stand-alone IP core clocks and the full design clocks to define the integrated

design timing constraints for the external clocks that drive CPRI IP core clocks

directly.

cpu_clk

clkin_50mhz

clk_ex_delay

pll1|clk[0]

map0_tx_clk

pll2|clk[0]

map0_rx_clk

pll2|clk[0]

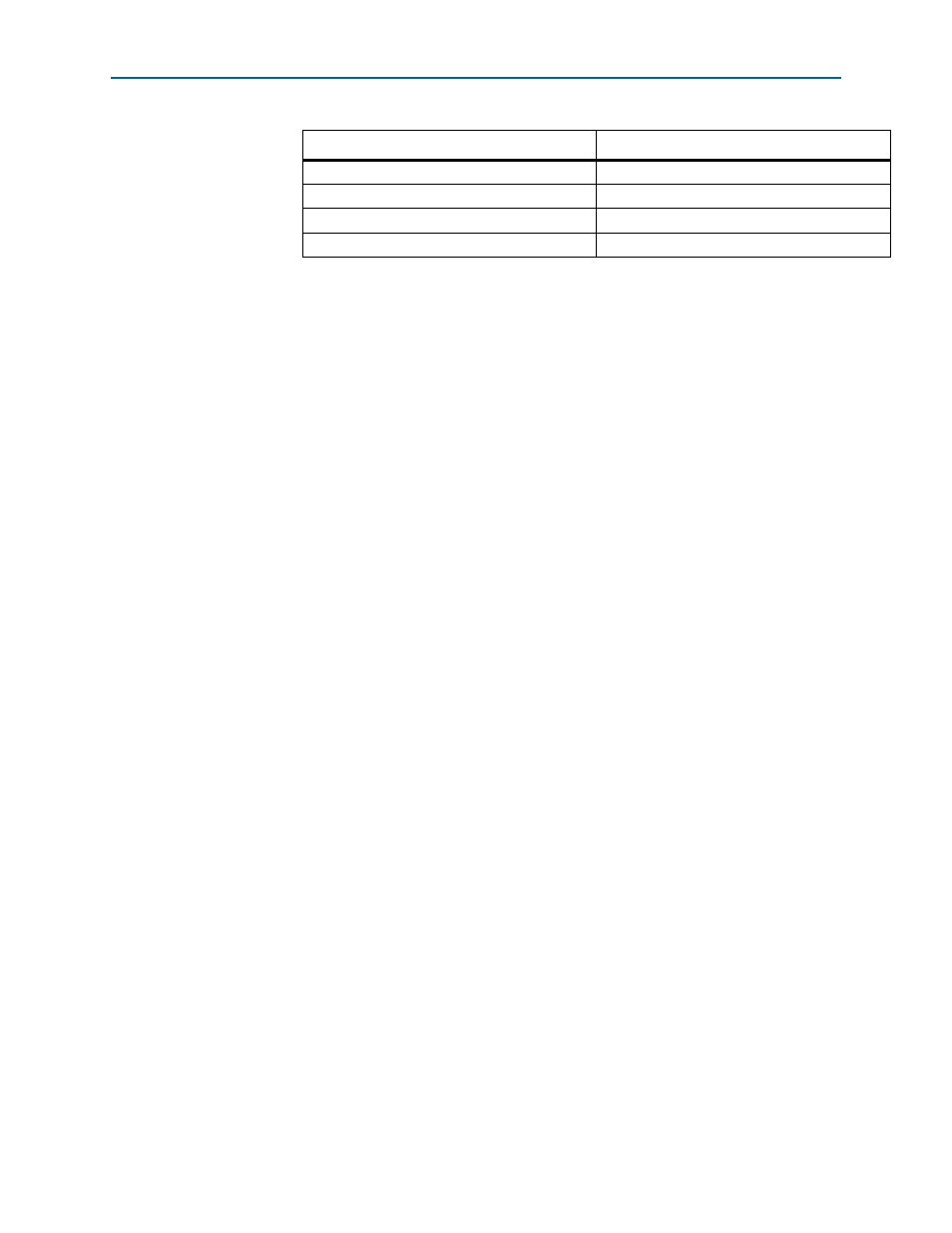

Table F–1. Stand-Alone IP Core Clock Names and Example Design Clock Names (Part 2 of 2)

Stand-Alone IP Core Clock Name

Full Design Clock Name