Altera CPRI IP Core User Manual

Page 198

E–20

Appendix E: Delay Measurement and Calibration

Single-Hop Delay Measurement

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

cycles of round-trip delay. The CPRI IP core adjusts the number of pipeline registers

the data passes through (in contrast to the number of registers it bypasses) to

compensate for mismatches between the desired round-trip delay programmed in the

cal_rtd

field, and the actual round-trip delay recorded in the

CPRI_ROUND_DELAY

register.

The

cal_status

field reports whether the CPRI IP core is successful in keeping the

round-trip delay at the value you prescribed in the

cal_rtd

field. The value of the

cal_status

bits should remain at 2’b11. If the value does not remain at 2’b11, you

should adjust the value in the

cal_rtd

field.Refer to

for the

full encoding of these status bits and how to determine whether to increase or

decrease the value of

cal_rtd

.

Initially, the number of pipeline registers the CPRI IP core uses is one half the total

number n of available register stages. This initial setting allows the CPRI IP core to

adjust the number up or down as required, and adds n/2+1 latency cycles to the Rx

path delay and the round-trip delay. The number of available register stages is five

and the default number of register stages of delay is three.

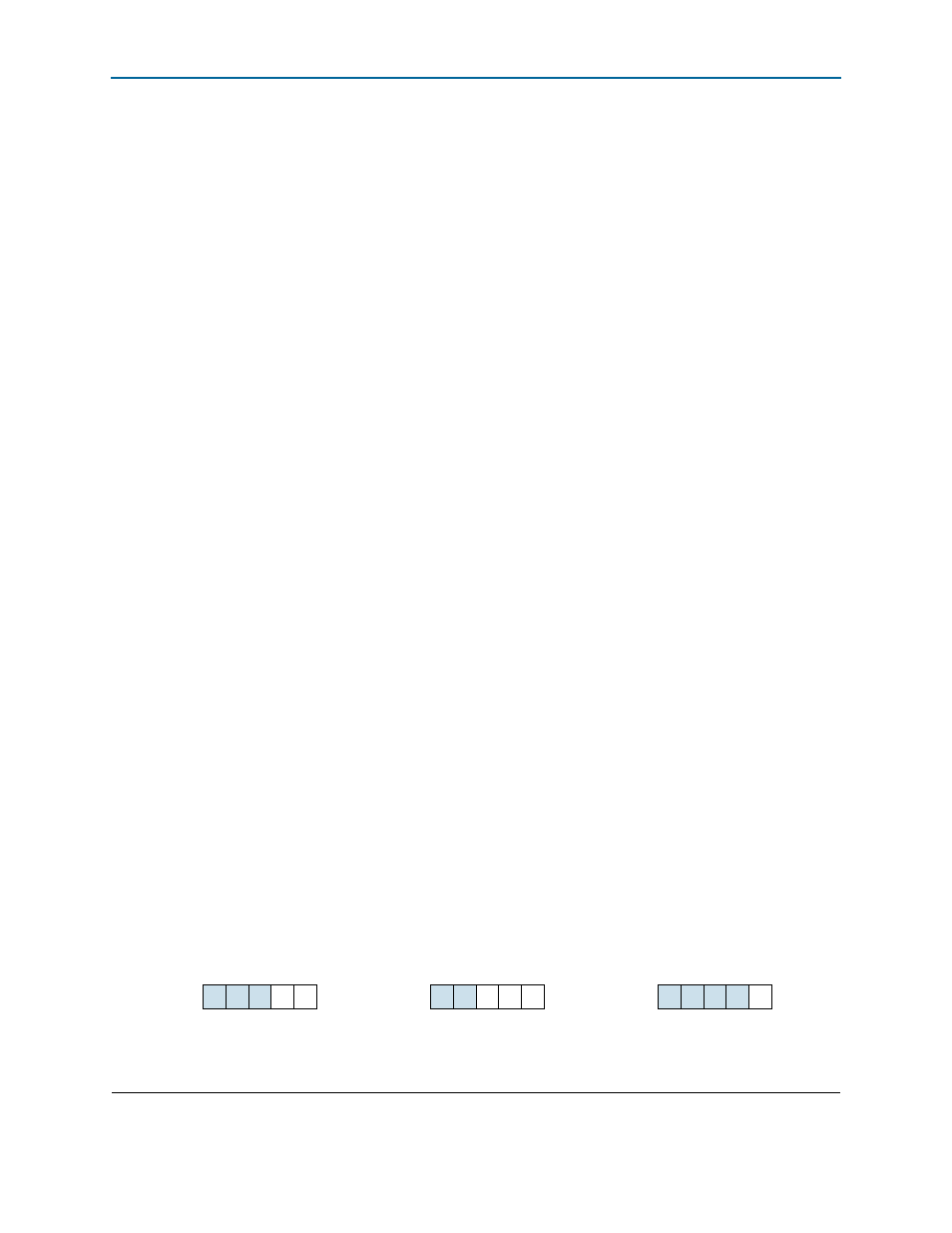

Figure E–7

shows two example behaviors of the autocalibration feature. In the

examples, the CPRI IP core changes the value of the pipeline read pointer in response

to a change in the measured actual round-trip delay through the IP core.

Figure E–7

shows the CPRI IP core in the following three states:

1. In the initial state, the CPRI IP core sets the read pointer for the pipeline registers

to the middle register.

2. In Case 1, the application writes the value of 60 in the

cal_rtd

field. When the

CPRI IP core measures the actual round-trip delay and sets the

rx_round_trip_delay

field in the

CPRI_ROUND_DELAY

register to the value of 61, the

CPRI IP core responds by moving the read pointer to decrease the pipeline length,

and therefore the measured round-trip delay value, by one

cpri_clkout

cycle. The

adjustment achieves the desired effect: the measured round-trip delay value

changes to 60.

3. In Case 2, the application writes the value of 62 in the

cal_rtd

field, instead. When

the CPRI IP core measures the actual round-trip delay and sets the

rx_round_trip_delay

field in the

CPRI_ROUND_DELAY

register to the value of 61, the

CPRI IP core responds by moving the read pointer to increase the pipeline length,

and therefore the measured round-trip delay value, by one

cpri_clkout

cycle. The

adjustment achieves the desired effect: the measured round-trip delay value

changes to 62.

Figure E–7. Round-Trip Delay Autocalibration Examples

Initial state:

Case 1:

Case 2:

Measured RTD = 61

Measured RTD = 61

cal_rtd = 60

cal_rtd = 62

1

2

3

4

5

1

2

3

4

5

1

2

3

4

5

—>

—>

—>

Rd pointer at 3

Rd pointer decrements to 2

Rd pointer increments to 4

—> Measured RTD = 60

—> Measured RTD = 62