Features, Physical layer architecture, Features –52 physical layer architecture –52 – Altera CPRI IP Core User Manual

Page 84: The physical layer has the following features, Frame synchronization, High-speed data serialization and deserialization, Clock and data recovery (receiver), 8b/10b encoding and decoding, Frame and control word assembly and delineation, Error detection

4–52

Chapter 4: Functional Description

CPRI Protocol Interface Layer (Physical Layer)

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

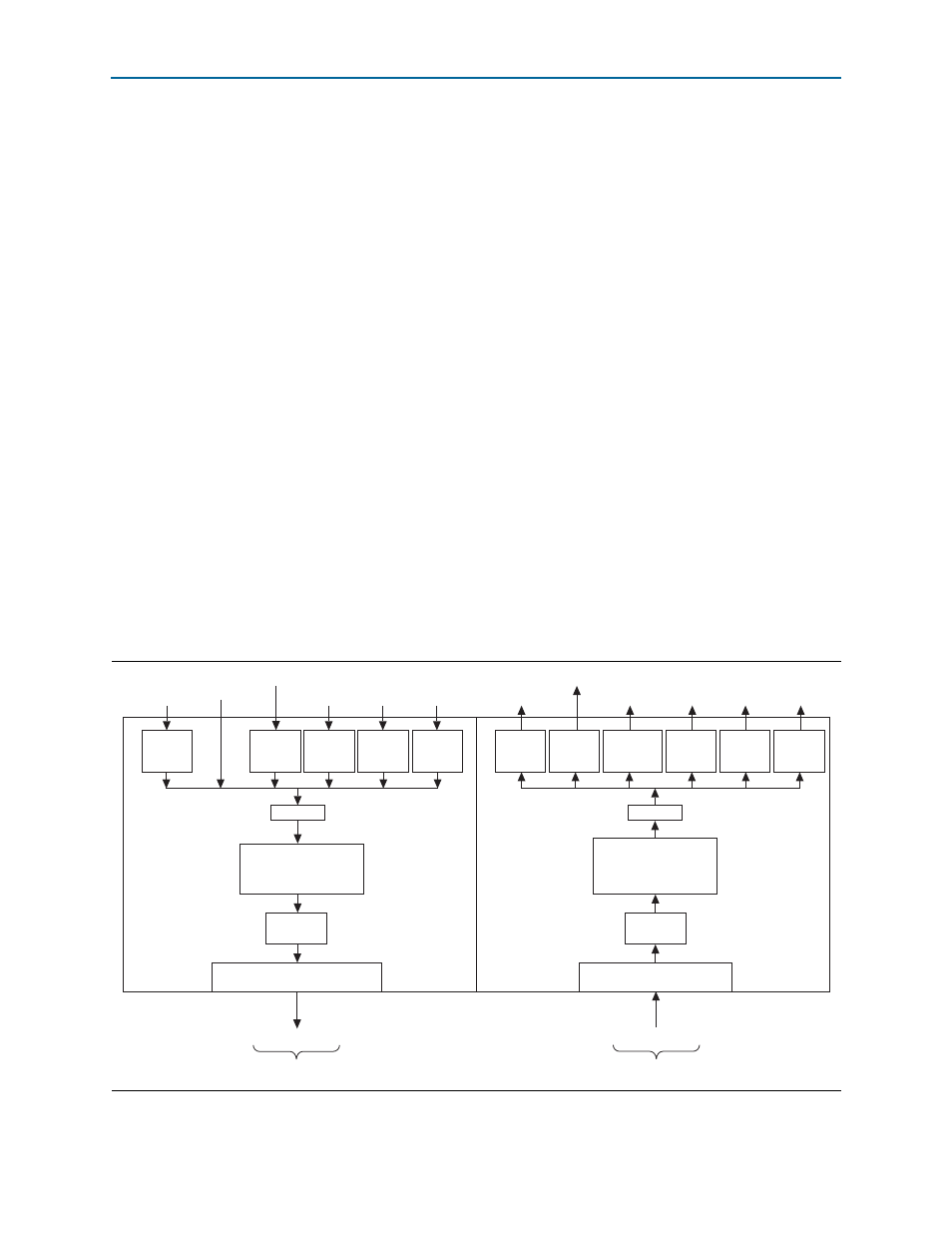

This section describes features and blocks of the CPRI protocol interface module.

Figure 4–26

shows a high-level block diagram of this module.

Features

The physical layer has the following features:

■

Frame synchronization

■

Transmitter and receiver with the following features:

■

High-speed data serialization and deserialization

■

Clock and data recovery (receiver)

■

8B/10B encoding and decoding

■

Frame and control word assembly and delineation

■

Error detection

■

Deterministic latency

■

So

ftware interface (status and control registers)

■

Error reporting

■

Clock decoupling

Physical Layer Architecture

Figure 4–26

shows the architecture of the physical layer.

Figure 4–26. Physical Layer High Level Block Diagram

tx_dataout

CPRI Link

rx_datain

CPRI Link

Receiver Transceiver

Rx State Machine

and

Frame Alignment

DEMUX

Payload

Timing

I/Q

Payload

RFN + HFN

Recovery

Ethernet

Decode

HDLC

Bit-Destuff

VSS/L1/

Alarms

Low-Level

Receiver

CPU IF

Module

HDLC_RX

ETH_RX

Timing

CPRI_RX_MAP

AUX IF

Module

Transmitter Transceiver

Tx State Machine

MUX

Payload

Ethernet

Encode

HDLC

Bit-Destuff

VSS/L1

Low-Level

Transmitter

CPU IF

Module

HDLC_TX

ETH_TX

Loop

Data

CPRI_TX_MAP

AUX IF

Module

I/Q

Payload

Rx

Elastic Buffer

Tx

Elastic Buffer