Map transmitter in synchronous buffer mode, Map transmitter in synchronous buffer mode –27 – Altera CPRI IP Core User Manual

Page 59

Chapter 4: Functional Description

4–27

MAP Interface

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

MAP Transmitter in Synchronous Buffer Mode

In the synchronized communication, called synchronous buffer mode, each AxC

interface has an incoming resynchronization signal,

mapN_tx_resync

. Application

software asserts this resynchronization signal synchronously with the

mapN_tx_clk

clock. When the application software asserts the resynchronization signal, it also

asserts the

mapN_tx_valid

signal and begins sending valid data on the

mapN_tx_data[31:0]

data bus for the individual AxC interface.

In synchronous buffer mode, the application should ignore the

mapN_tx_ready

output

signals. However, it should assert the

mapN_tx_valid

input signals when sending

valid data. The CPRI IP core holds the

mapN_tx_ready

output signals high. The

application must assert the

mapN_tx_valid

input signals when or immediately after it

asserts the

mapN_tx_resync

signals. However, if the application does not assert the

mapN_tx_valid

input signals in the same cycle as the

mapN_tx_resync

signals, and

subsequently reasserts

mapN_tx_resync

while

mapN_tx_valid

is still high, data in

transition through the MAP Tx interface buffer is lost.

1

Altera recommends that your application assert the

mapN_tx_valid

input signals

when it asserts the

mapN_tx_resync

signals.

For details about the behavior of the individual signals in synchronous buffer mode,

refer to

“MAP Transmitter Signals” on page 6–3

shows the expected typical behavior of the MAP Tx signals in this

synchronization mode. In this example, the CPRI line rate is 2457.6 Mbps. The

cpri_tx_start

signal is asserted for the duration of a single frame, and the CPRI line

rate determines the duration of a basic frame in

cpri_clkout

cycles. At 2457.6 Mbps, a

basic frame is 16

cpri_clkout

cycles. At this line rate, as shown in

Table 4–2 on

page 4–10

, the

cpri_clkout

frequency is 61.44 MHz. The

mapN_tx_clk

frequency is

7.68 MHz (oversampling rate 2), approximately 0.125 times the

cpri_clkout

frequency.

1

To ensure IP core control over the resynchronization signal timing, Altera

recommends that your application trigger the

mapN_tx_resync

signal with the CPRI

IP core output signal

cpri_tx_start

. The CPRI AUX interface asserts the

cpri_tx_start

signal according to the offset value specified in the

user-programmable

CPRI_START_OFFSET_TX

register.

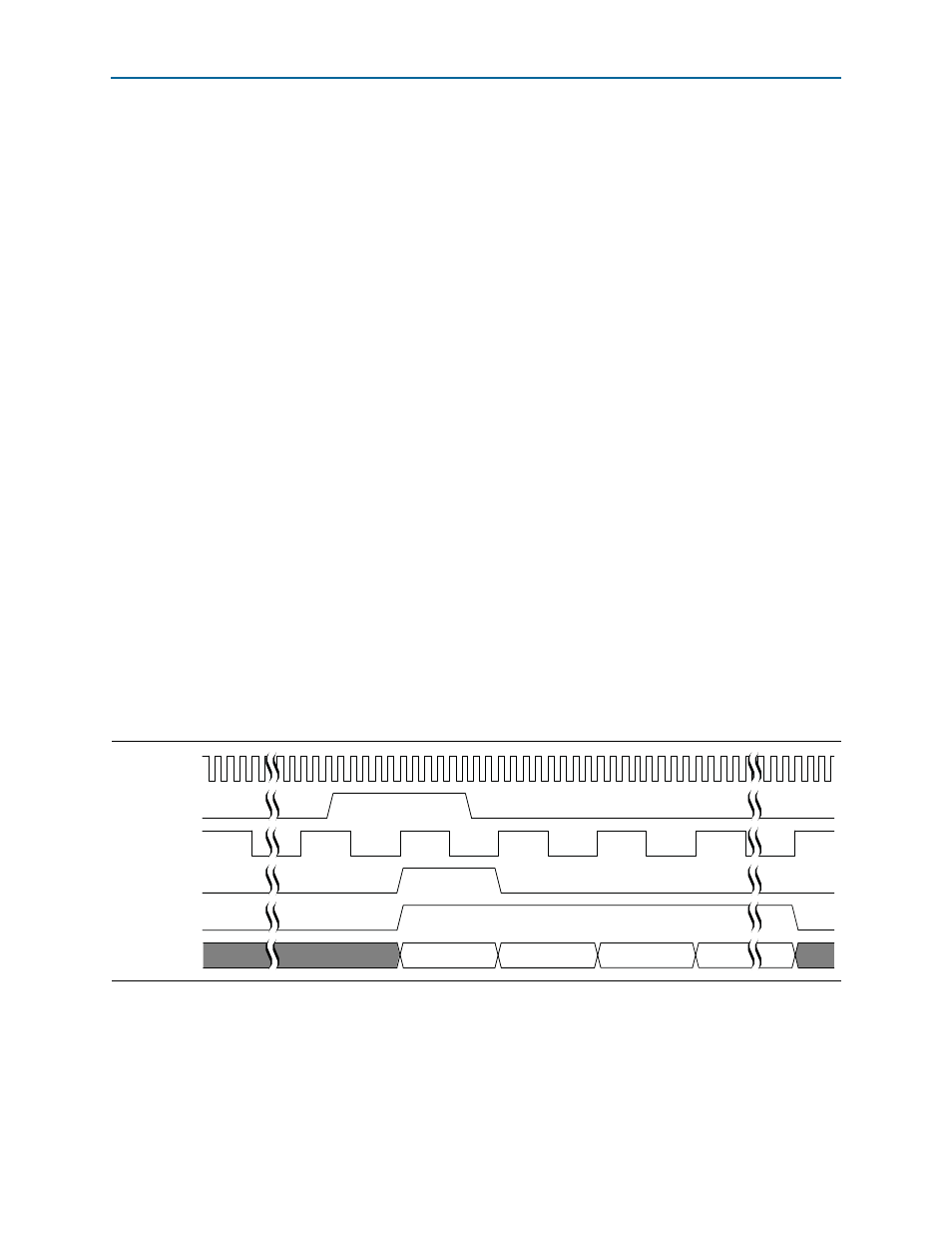

Figure 4–14. MAP Transmitter Interface in Synchronous Buffer Mode

cpri_clkout

cpri_tx_start

mapN_tx_clk

mapN_tx_resync

mapN_tx_valid

mapN_tx_data[31:0]