Altera CPRI IP Core User Manual

Page 57

Chapter 4: Functional Description

4–25

MAP Interface

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

MAP transmitter communication on the individual data map interfaces coordinates

the transfer of data according to one of three different synchronization modes. The

synchronization mode is determined by your selection in the CPRI parameter editor

and by the value you program in the

map_tx_sync_mode

field of the

CPRI_MAP_CONFIG

register (

Table 4–10

.

lists the clocks for the AxC interfaces in the different Tx synchronization

modes.

You determine the AxC interface clocks when you turn the Enable MAP interface

synchronization with core clock parameter

on (SYNC_MAP = 1) or off (SYNC_MAP

= 0) in the CPRI parameter editor before you generate your CPRI IP core.

MAP Transmitter Interface Signals in Different Synchronization Modes

The different CPRI IP core MAP synchronization modes use different interface

signals.

lists the MAP transmitter interface signals used in each of these

modes. Table notes indicate the correct interpretation of the different symbols.

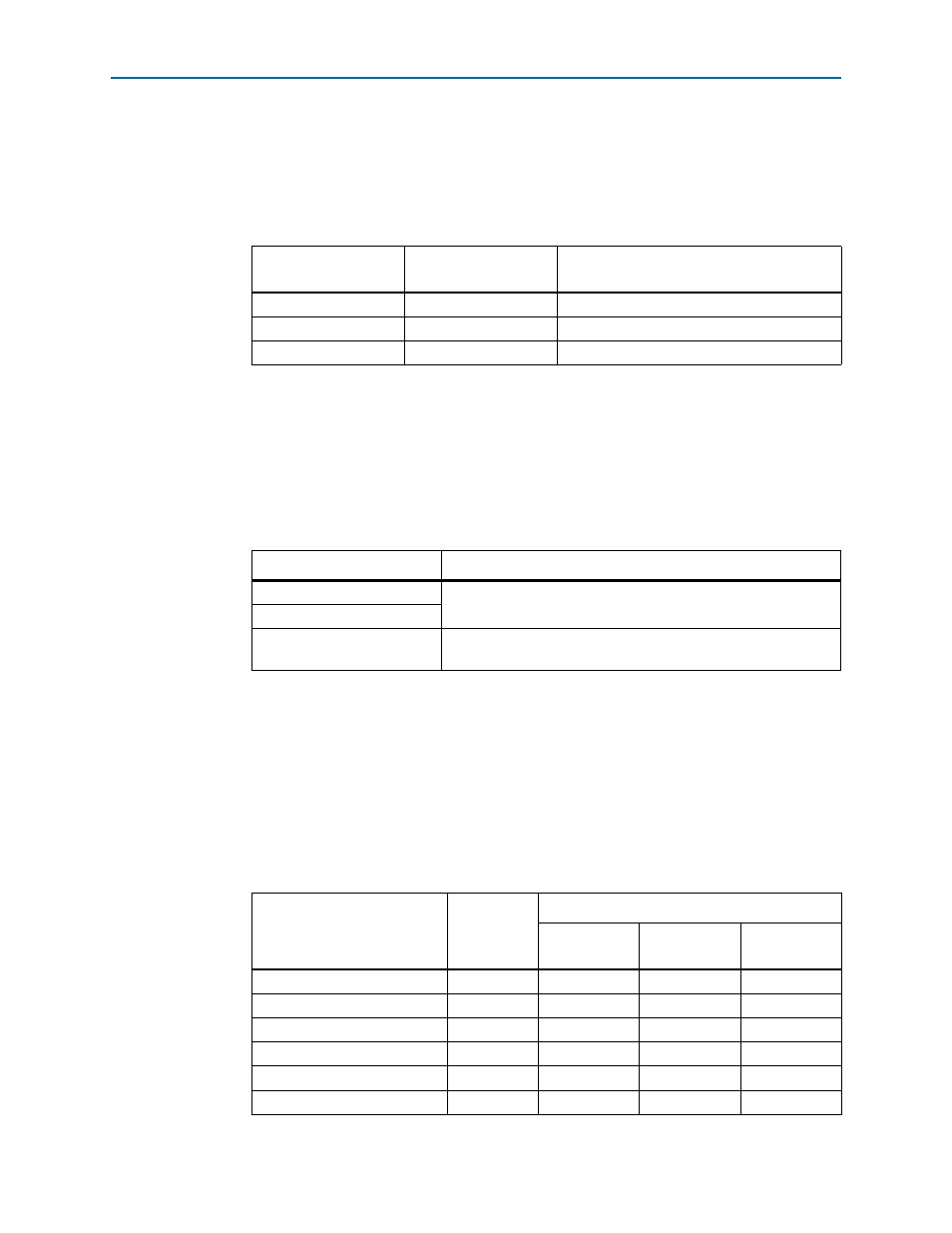

Table 4–10. MAP Tx Synchronization Mode Determined by CPRI_MAP_CONFIG Register Bits

SYNC_MAP

(1)

map_tx_sync_mode

(register bit [3])

Tx Synchronization Mode

0

0

0

1

Synchronous buffer mode (

)

1

—

(2)

Internally-clocked mode (

)

Notes to

Table 4–10

:

(1) You determine the value of SYNC_MAP when you generate your CPRI IP core. Refer to

(2) When SYNC_MAP has the value of 1, the value in the

map_tx_sync_mode

bit of the

CPRI_MAP_CONFIG

register

is ignored.

Table 4–11. MAP Tx Interface Clocks Determined by Tx Synchronization Mode

Tx Synchronization Mode

AxC Channel Clocks

FIFO mode

Each AxC Tx interface is clocked by its own

mapN_tx_clk

clock

driven by the application.

Synchronous buffer mode

Internally-clocked mode

Every AxC interface is clocked by the CPRI IP core clock,

cpri_clkout

.

Table 4–12. MAP Transmitter Interface Signals by Synchronization Mode

(Part 1 of 2)

Signal Name

Direction

Available in Synchronization Mode

FIFO

Synchronous

Buffer

Internally

Clocked

map{23…0}_tx_clk

Input

v

v

—

map{23…0}_tx_reset

Input

v

v

—

map{23…0}_tx_valid

Input

v

v

v

map{23…0}_tx_data[31:0]

Input

v

v

v

map{23…0}_tx_ready

Output

v

v

map{23…0}_tx_resync

Input

—

v

—