Megacore verification, Performance and resource utilization – Altera CPRI IP Core User Manual

Page 12

1–6

Chapter 1: About This MegaCore Function

MegaCore Verification

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

MegaCore Verification

Before releasing a version of the CPRI IP core, Altera runs comprehensive regression

tests in the current version of the Quartus

®

II software. These tests use the

MegaWizard

™

Plug-In Manager to create the instance files. Altera tests these files in

simulation and hardware to confirm functionality.

Altera tests and verifies the CPRI IP core in hardware, especially the deterministic

latency feature, for different platforms and environments.

Performance and Resource Utilization

This section contains tables showing IP core variation size and performance examples.

For resource utilization information for additional CPRI IP core variations, refer to the

reports the Quartus II software generates during compilation.

lists the resources and expected performance for CPRI IP core variations

configured with the following features:

■

Operate in REC master mode

■

Include autorate negotiation support

■

Provide Ethernet access through the MI interface

■

Do not provide an HDLC block

■

Use Basic mapping mode

■

Clock the AxC channels with independent clocks (the Enable MAP interface

synchronization with core clock

parameter is turned off)

■

Do not include automatic round-trip delay calibration logic

■

Do not include VSS access through the CPU interface

The numbers of ALMs and logic registers are rounded up to the nearest 100.

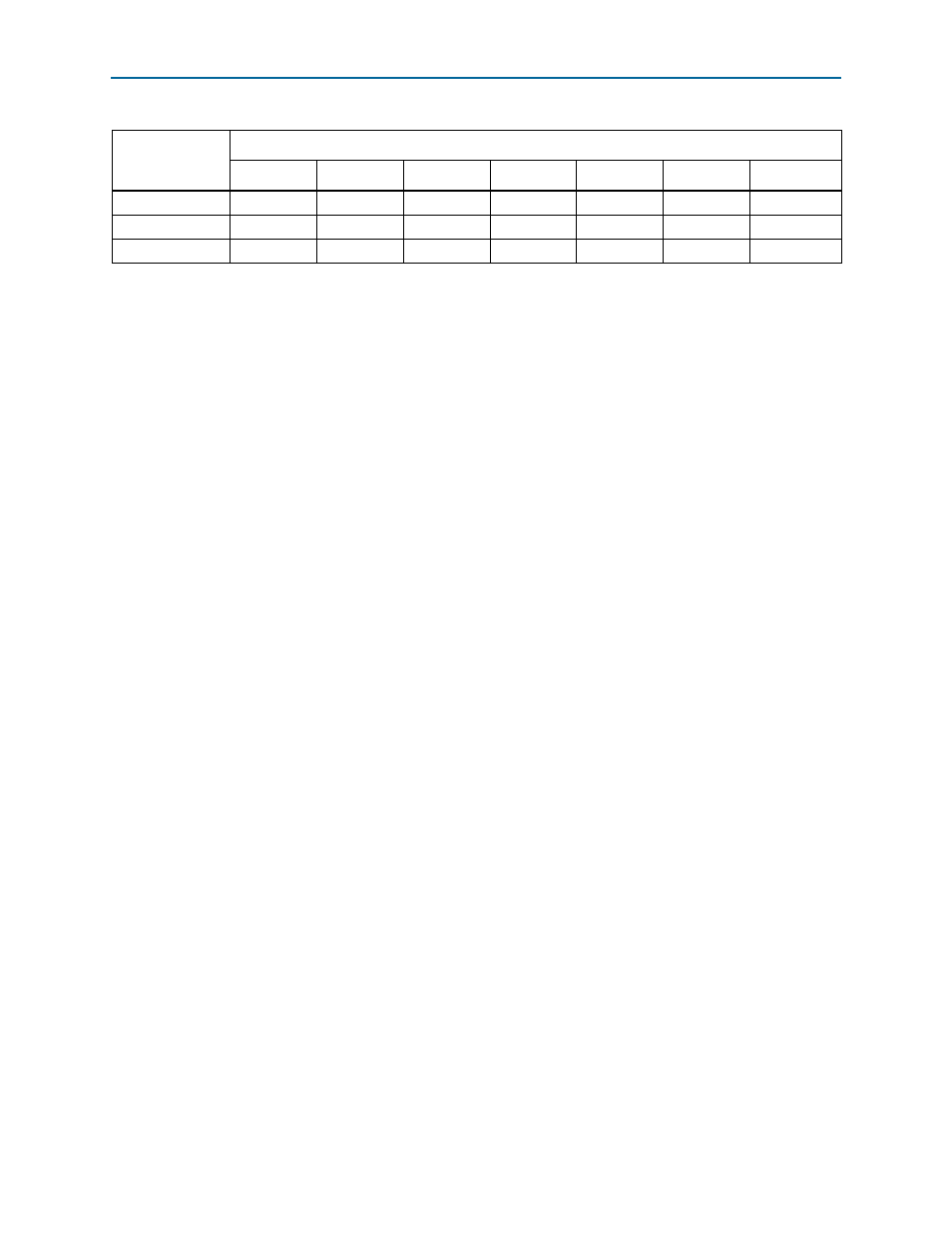

Arria II GZ

–4

–4

–4

–4

–3

–3

(3)

Cyclone V GX

C8

–7

–7

–7

(3)

(3)

(3)

Cyclone IV GX

C8, I7

C8, I7

C8, I7

–7

(3)

(3)

(3)

Notes to

Table 1–3

:

(1) The entry

–

x indicates that both the industrial speed grade Ix and the commercial speed grade Cx are supported for this device family and CPRI

line rate.

(2) Only the I3 speed grade is available for a CPRI IP core that runs at this line rate and targets the Arria II GX device family.

(3) This CPRI line rate is not supported for this device family.

(4) Altera recommends that for designs that include a 9.8304 Gbps CPRI IP core variation that targets an Arria V GT device, you use multiple seeds

in the Quartus II Design Space Explorer to find the optimal Fitter settings to meet the timing constraints. Following the Timing Advisor's

recommendations, including optimizing for speed and using LogicLock regions may be necessary to meet timing, especially for more complex

variations implemented in the largest devices.

Table 1–3. Slowest Recommended Device Family Speed Grades

(1)

(Part 2 of 2)

Device Family

or Variant

CPRI Line Rate (Mbps)

614.4

1228.8

2457.6

3072.0

4915.2

6144

9830.4