Clock and reset interface signals, Clock and reset interface signals –17, Table 6–15 – Altera CPRI IP Core User Manual

Page 115

Chapter 6: Signals

6–17

Clock and Reset Interface Signals

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

In addition to customization of the transceiver through the transceiver parameter

editor, you can use the transceiver reconfiguration block to dynamically modify the

parameter interface. The dynamic reconfiguration block lets you reconfigure the

following PMA settings:

■

Pre-emphasis

■

Equalization

■

Offset cancellation

■

V

OD

on a per channel basis

1

You must configure the dynamic reconfiguration block in any CPRI design that

targets an Arria II GX, Arria II GZ, Cyclone IV GX, or Stratix IV GX device.

f

For more information about the transceiver reconfiguration block and about offset

cancellation, refer to the appropriate device handbook.

Clock and Reset Interface Signals

describes the CPRI IP core clock and reset signals not described in other

sections with their associated modules.

gxb_rx_errdetect[1:0]

Output

Transceiver 8B/10B code group violation or disparity error indicator. If either

bit is high, a code group violation or disparity error was detected on the

associated received code group. Use the

gxb_rx_disperr

signal to

determine whether this signal indicates a code group violation or a disparity

error. For details, refer to the relevant device handbook.

Note to

Table 6–14

:

(1) Refer to

“Instantiating Multiple CPRI IP Cores” on page 2–6

for information about how to successfully combine multiple high-speed transceiver

channels—whether in two CPRI IP core instances or in a CPRI IP core and in another component—in the same quad.

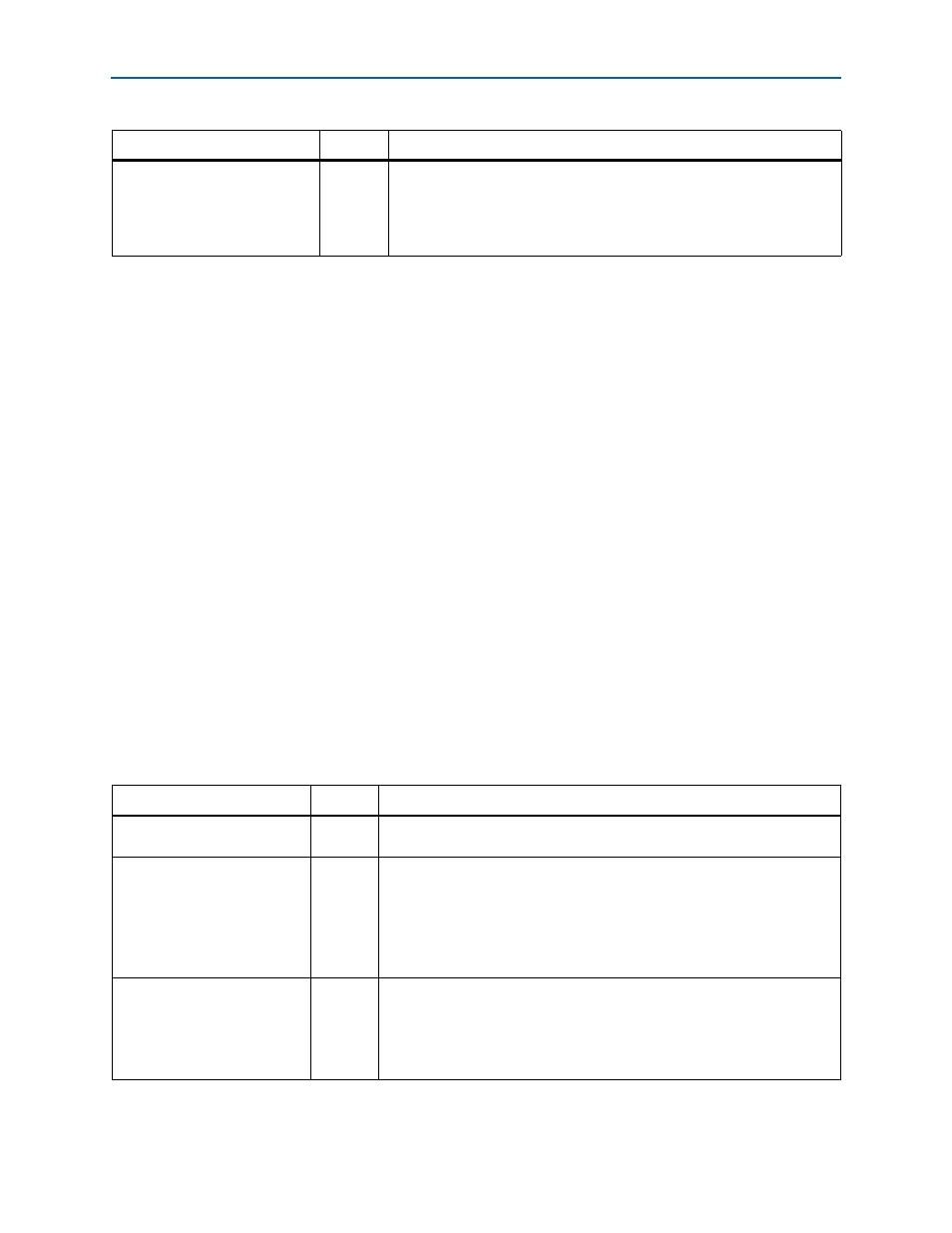

Table 6–14. Transceiver Signals (Part 3 of 3)

Signal Direction

Description

Table 6–15. CPRI IP Core Clock and Reset Signals (Part 1 of 2)

Signal Direction

Description

clk_ex_delay

Input

Extended delay measurement clock. This clock must be driven from a

common source with the transceiver reference clock.

reset_ex_delay

Input

Reset for extended delay measurement block.This reset is associated with the

clk_ex_delay

clock.

reset_ex_delay

can be asserted asynchronously, but must stay asserted at

least one clock cycle and must be de-asserted synchronously with the clock

with which it is associated. Refer to

for a circuit that

shows how to enforce synchronous deassertion of a reset signal.

config_reset

Input

Register reset. This reset is associated with the

cpri_clkout

clock.

config_reset

can be asserted asynchronously, but must stay asserted at

least one clock cycle and must be de-asserted synchronously with the clock

with which it is associated. Refer to

for a circuit that

shows how to enforce synchronous deassertion of a reset signal.