Table 7–6 on, Table 7–6 – Altera CPRI IP Core User Manual

Page 120

7–4

Chapter 7: Software Interface

CPRI Protocol Interface Registers

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

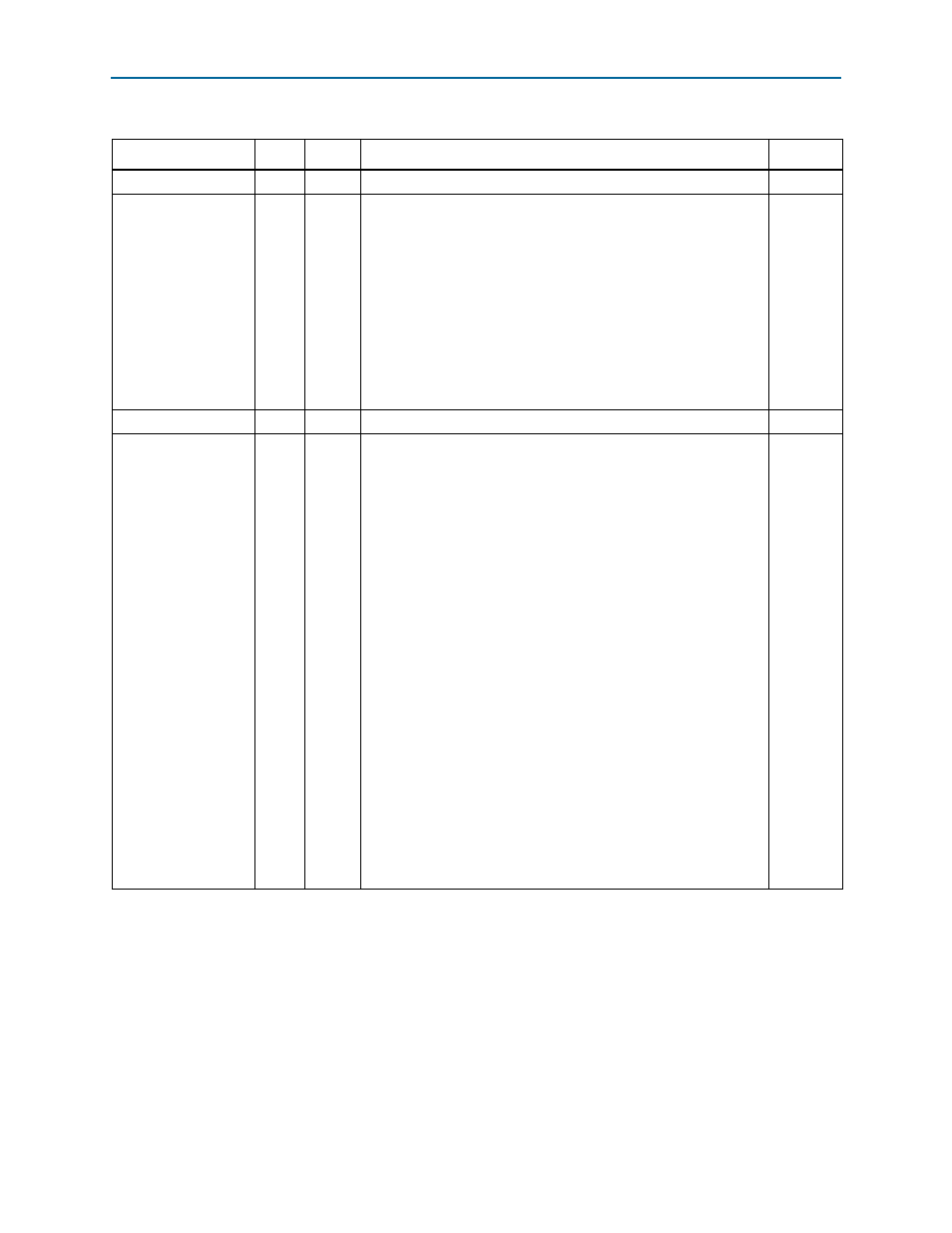

Table 7–6. CPRI_CONFIG—CPRI Configuration—Offset: 0x8 (Part 1 of 2)

Field

Bits

Access

Function

Default

RSRV

[31:7]

UR0

Reserved.

26'h0

tx_enable_force

[6]

RW

Enables the RE slave testing feature described in

Synchronization Without an REC Master” on page 5–4

. Specifies

whether the CPRI RE slave should attempt to achieve link

synchronization without a CPRI link connection to a CPRI master.

1’b0—The RE slave self-synchronization testing feature is not

activated.

1’b1—The RE slave self-synchronization testing feature is

activated. This value is only valid if the CPRI IP core is configured

in slave clocking mode. Refer to

“Achieving Link Synchronization

Without an REC Master” on page 5–4

for required conditions for

this testing feature.

1’h0

tx_enable

[5]

RW

Enable transmission on CPRI link.

1’h0

loop_mode

[4:2]

RW

Testing loopback mode. The reverse loopback paths specified in this

register field include the transmission framing block, in contrast to

the lower-level loopback path specified in the

CPRI_PHY_LOOP

register at offset 0x24. The loopback paths specified in this register

field are only enabled after frame synchronization, and can only be

activated in a CPRI RE slave. The following field values are defined:

000: No loopback.

001: Full CPRI frame loop. Incoming CPRI data and control words

are sent back in outgoing CPRI communication.

010: IQ sample loop. Incoming CPRI data are sent back in

outgoing CPRI communication; control words are generated

locally.

011: Fast C&M loop. Incoming CPRI C&M control and data words

are sent back in outgoing CPRI communication; remaining data

and control words are generated locally.

100: Fast C&M and VSS loop. Incoming CPRI C&M and

vendor-specific control words are sent back in outgoing CPRI

communication; data and remaining control words are generated

locally.

Note that this loopback mode is superseded by the 1-bit physical

layer loop mode specified in the

CPRI_PHY_LOOP

register at

offset 0x24. If both register fields hold non-zero values, the value

in the

CPRI_PHY_LOOP

register takes precedence.

3'h0