Reset, frame synchronization, and initialization – Altera CPRI IP Core User Manual

Page 152

8–4

Chapter 8: CPRI IP Core Demonstration Testbench

Reset, Frame Synchronization, and Initialization

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

Reset, Frame Synchronization, and Initialization

The reset sequence is simple—all of the reset signals for the CPRI IP core, except

gxb_powerdown,

are asserted at the beginning of the simulation, are kept high for 500

gxb_refclk

clock cycles, and are then deasserted. The following reset signals are

asserted:

■

reset

■

reset_ex_delay

■

cpu_reset

■

config_reset

■

mapN_tx_reset

for N={0...23}

■

mapN_rx_reset

for N={0...23}

Next, the testbench performs basic programming of the CPRI IP core internal

registers, to allow CPRI communication.

testbench programs. For a full description of each register, refer to

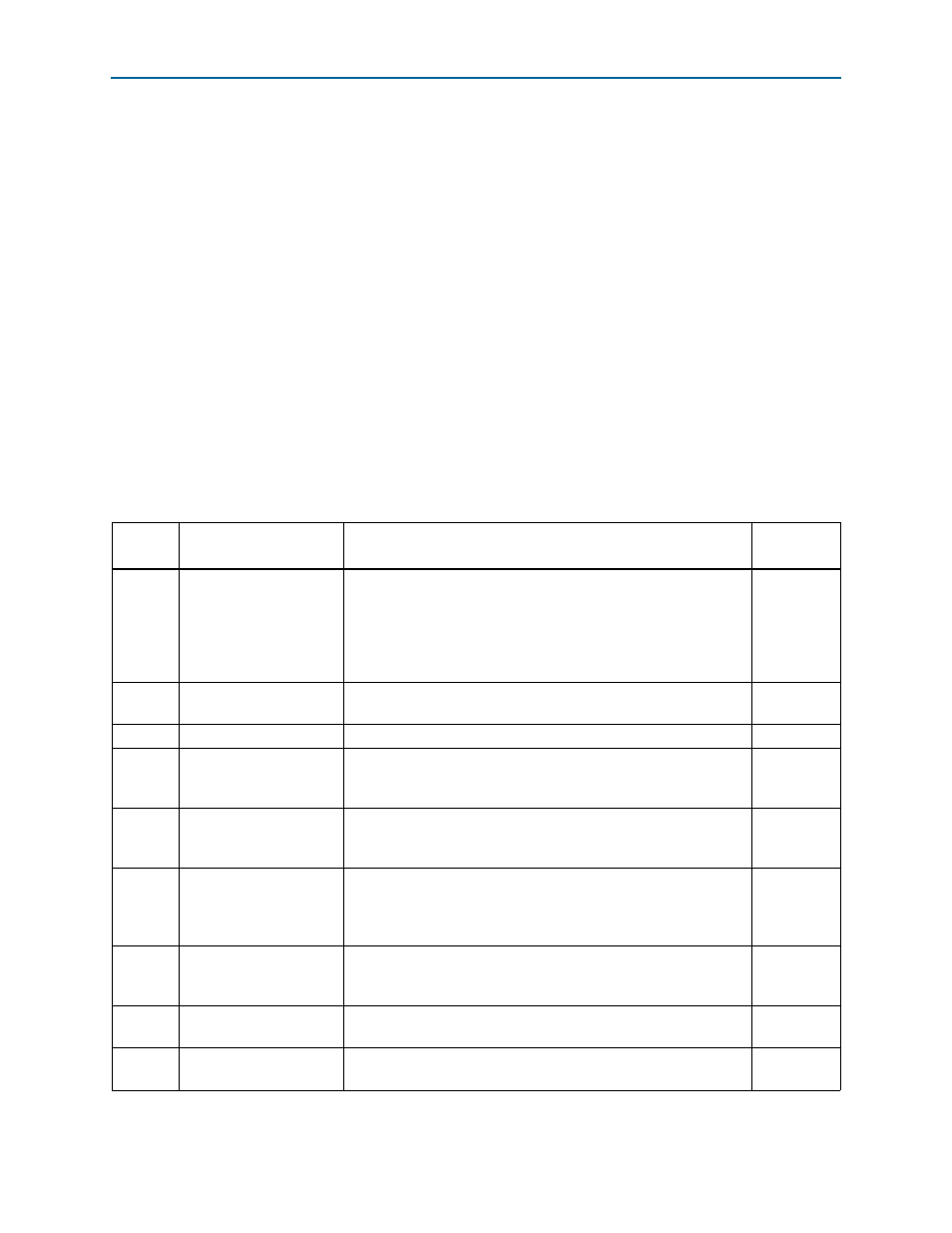

Table 8–3. Testbench Register Settings

Register

Address

Register Name

Description

Value

0x0058

CPRI_TX_PROT_VER

Set the CPRI protocol version. If the IP core is configured with CPRI

line rate 3.072 Gbps or lower, the testbench sets this register to the

value of 0x1 to indicate the transmissions are not scrambled. If the

IP core is configured with CPRI line rate greater than 3.072 Gbps,

the testbench sets this register to the value of 0x2 to indicate

outgoing transmissions are scrambled.

0x00000001

or

0x00000002

depending

on the CPRI

line rate

0x005C

CPRI_TX_SCR_SEED

Set the scrambling seed. This register is ignored when

transmissions are not scrambled.

0x0000000F

0x003C

CPRI_EX_DELAY_CONFIG

For extended delay measurement, set the N value to decimal 127.

0x0000007F

0x0008

CPRI_CONFIG

Enable CPRI control word insertion, set the CPRI MegaCore to use

master clocking mode, set loop_mode to No internal loopback, and

enable transmission on the CPRI link.

0x00000021

0x0100

CPRI_MAP_CONFIG

If the IP core is configured with a MAP interface, set map_mode to

basic mapping scheme, set MAP transmiter and receiver

synchronization mode to FIFO mode, and use 16-bit sample width.

0x00000000

0x0104

CPRI_MAP_CNT_CONFIG

If the IP core is configured with a MAP interface, set number of

active data channels and set the oversampling factor to 1 (sampling

rate is 3.84 MHz). The value depends on the configured number of

antenna-carrier interfaces.

Depends on

configured

values

0x0308

HDLC_CONFIG

If the IP core is configured with an HDLC block, set the HDLC

communication to little endian format and turn off various other

HDLC block capabilities.

0x00000000

0x030C

HDLC_CONFIG_2

If the IP core is configured with an HDLC block, enable CRC

insertion in the HDLC frames the IP core transmits.

0x00000001

0x032C

HDLC_CONFIG_3

If the IP core is configured with an HDLC block, set the HDLC TX

logic in store-and-forward mode.

0x00000001