Altera CPRI IP Core User Manual

Page 114

6–16

Chapter 6: Signals

Physical Layer Signals

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

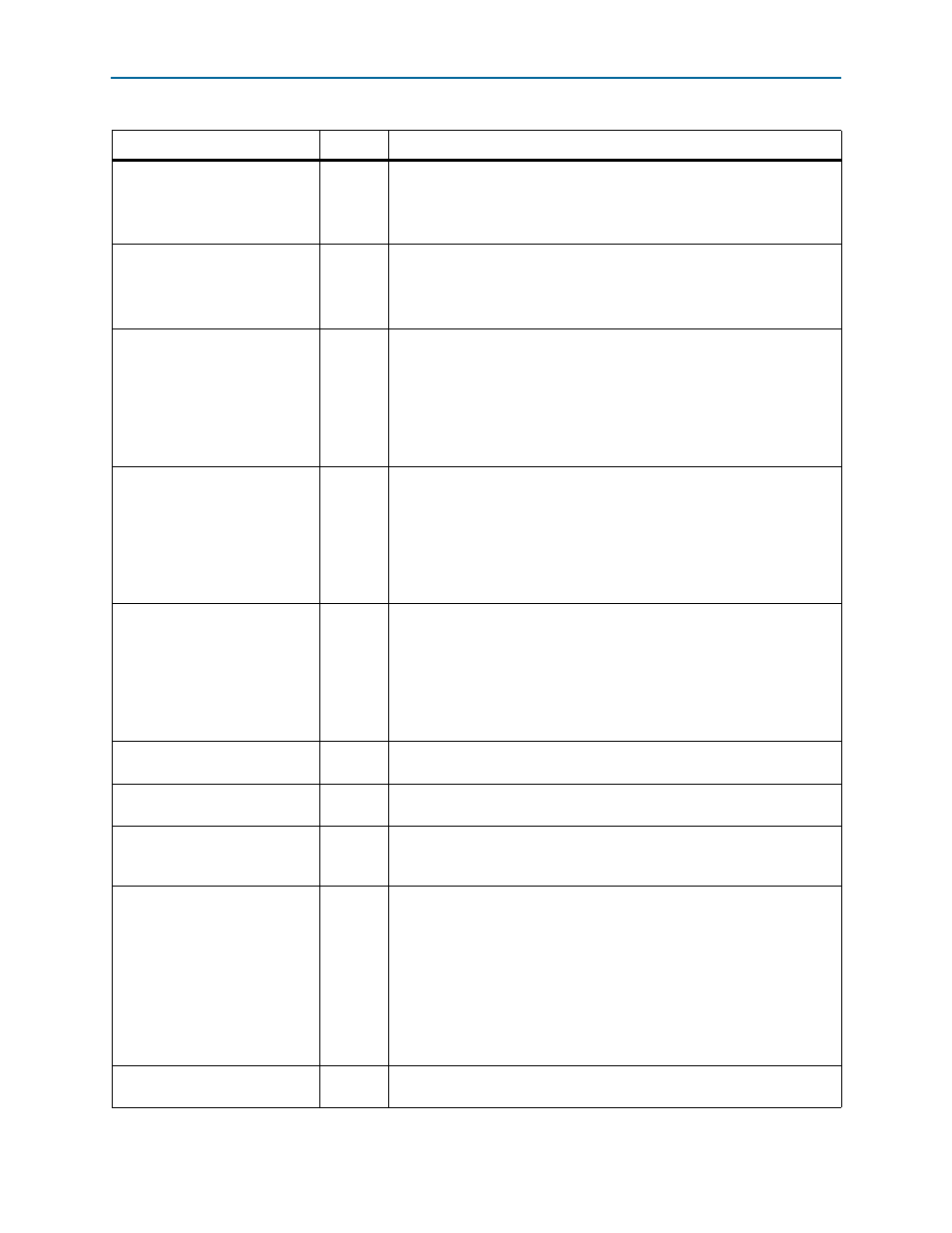

reconfig_fromgxb_s_rx

[16:0]

(

[4:0]

for

Cyclone IV GX devices)

Output

Driven to an external dynamic reconfiguration block from the slave receiver

transceiver block. The bus identifies the transceiver channel whose settings

are being transmitted to the dynamic reconfiguration block.

This signal is not present in Arria V, Cyclone V, and Stratix V variations.

reconfig_fromgxb_m

[16:0]

(

[4:0]

for

Cyclone IV GX devices)

Output

Driven to an external dynamic reconfiguration block from the master

transceiver block. The bus identifies the transceiver channel whose settings

are being transmitted to the dynamic reconfiguration block.

This signal is not present in Arria V, Cyclone V, and Stratix V variations.

reconfig_busy

Input

Indicates the busy status of the dynamic reconfiguration controller. After the

device powers up, this signal remains low for the first

reconfig_clk

clock

cycle. It is then asserted and remains high while the dynamic

reconfiguration controller performs offset cancellation on all the receiver

channels connected to the ALTGX_RECONFIG instance. This signal is

deasserted when offset cancellation completes successfully.

This signal is not present in Arria V, Cyclone V, and Stratix V variations.

reconfig_write

Input

Indicates the user is writing to the dynamic reconfiguration controller to

implement the autorate negotiation feature. Asserting this signal instructs

the CPRI reset controller to perform the reset sequence for dynamic

reconfiguration of the transceiver. For details about dynamic

reconfiguration, refer to the relevant device handbook.If you are not using

the autorate configuration feature, you must tie this input to 0.

This signal is not present in Arria V, Cyclone V, and Stratix V variations.

reconfig_done

Input

Indicates the dynamic reconfiguration controller has completed the

reconfiguration operation. Asserting this signal instructs the CPRI reset

controller to complete the reset sequence for dynamic reconfiguration of the

transceiver. For details about dynamic reconfiguration, refer to the relevant

device handbook. If you are not using the autorate negotiation feature, you

must tie this input to 0.

This signal is not present in Arria V, Cyclone V, and Stratix V variations.

gxb_pll_locked

Output

Indicates the transceiver transmitter PLL is locked to the input reference

clock. This signal is asynchronous.

gxb_rx_pll_locked

Output

Indicates the transceiver CDR is locked to the input reference clock. This

signal is asynchronous.

gxb_rx_freqlocked

Output

Transceiver clock data recovery (CDR) lock mode indicator. If this signal is

high, the transceiver CDR is in lock-to-data (LTD) mode. If this signal is low,

the transceiver CDR is in lock-to-reference clock (LTR) mode.

gxb_powerdown

Input

Transceiver block power down. This signal resets and powers down all

analog and digital circuitry in the transceiver block, including physical

coding sublayer (PCS), physical media attachment (PMA), clock multiplier

unit (CMU) channels, and central control unit (CCU). This signal does not

affect the

gxb_refclk

buffers and reference clock lines.

All the

gxb_powerdown

input signals of IP cores intended to be placed in

the same quad must be tied together. The

gxb_powerdown

signal must be

tied low or must remain asserted for at least 2 ms whenever it is asserted.

This signal is not present in ArriaV, Cyclone V, and Stratix V variations.

gxb_rx_disperr[1:0]

Output

Transceiver 8B/10B disparity error indicator. If either bit is high, a disparity

error was detected on the associated received code group.

Table 6–14. Transceiver Signals (Part 2 of 3)

Signal Direction

Description