Ough, Table 7–81 – Altera CPRI IP Core User Manual

Page 147

Chapter 7: Software Interface

7–31

HDLC Registers

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

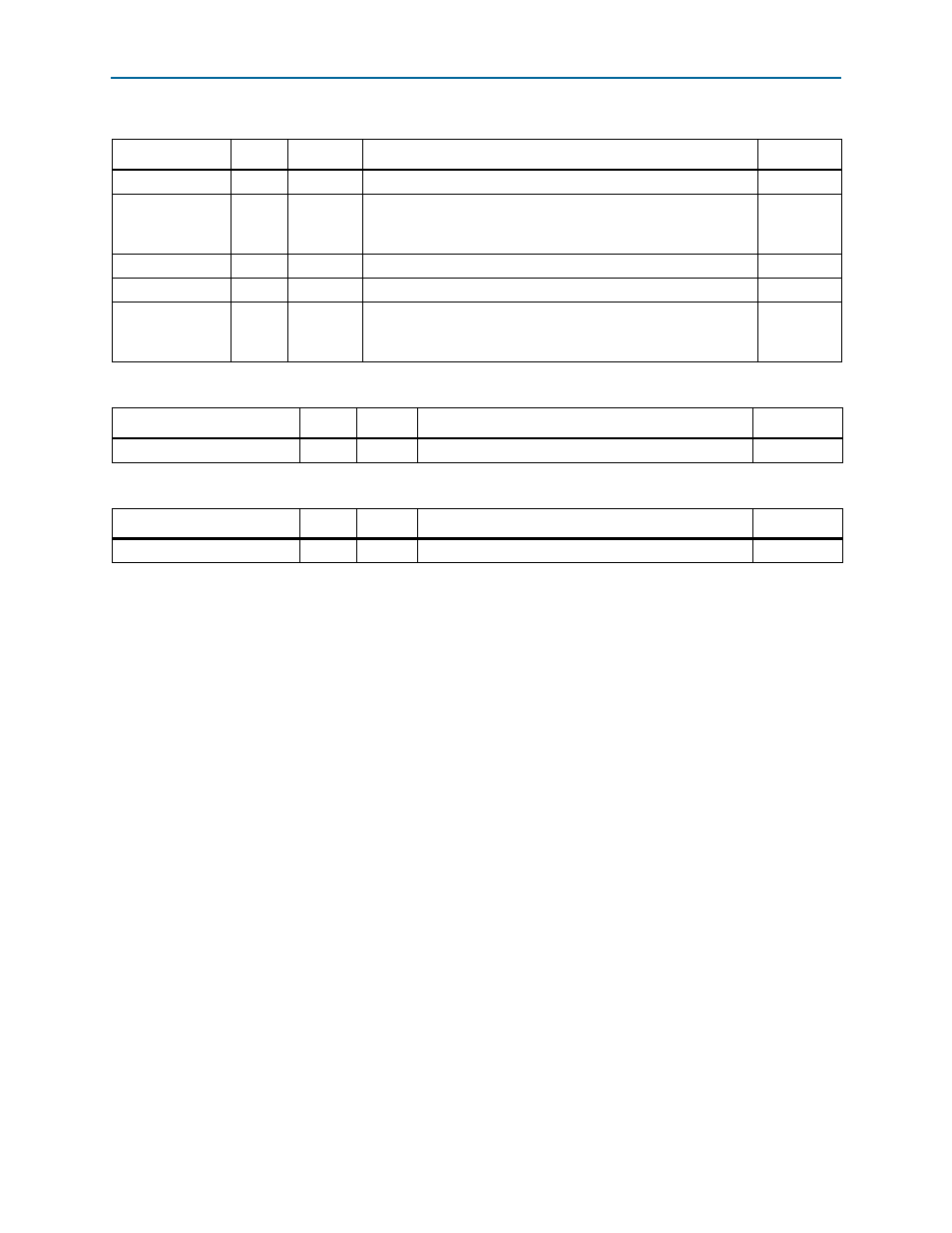

Table 7–79. HDLC_CONFIG_3—HDLC Feature Configuration 3—Offset: 0x32C

Field

Bits

Access

Function

Default

RSRV

[31:17] UR0

Reserved.

15’h0

tx_start_thr

[16:8]

RW

Transmit start threshold. If store-and-forward mode is disabled,

transmission to the CPRI link starts when this number of 32-bit

words are stored in the Tx buffer.

9’h004

RSRV

[7:2]

UR0

Reserved.

5’h0

rx_crc_en

[1]

RW

Indicates that CRC checking is enabled.

1'h0

tx_st_fwd

[0]

RW

Transmit store-and-forward mode. In store-and-forward mode, a

full packet is stored before transmission starts. Packets longer

than the Tx buffer are aborted.

1'h0

Table 7–80. HDLC_CNT_RX_FRAME—HDLC Receiver Module Frame Counter—Offset: 0x330

Field

Bits

Access

Function

Default

hdlc_cnt_rx_frame

[31:0]

RO

Number of frames received from the CPRI receiver.

32'h0

Table 7–81. HDLC_CNT_TX_FRAME—HDLC Transmitter Module Frame Counter—Offset: 0x334

Field

Bits

Access

Function

Default

hdlc_cnt_tx_frame

[31:0]

RO

Number of frame transmitted to the CPRI transmitter.

32'h0