Altera CPRI IP Core User Manual

Page 96

5–4

Chapter 5: Testing Features

Achieving Link Synchronization Without an REC Master

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

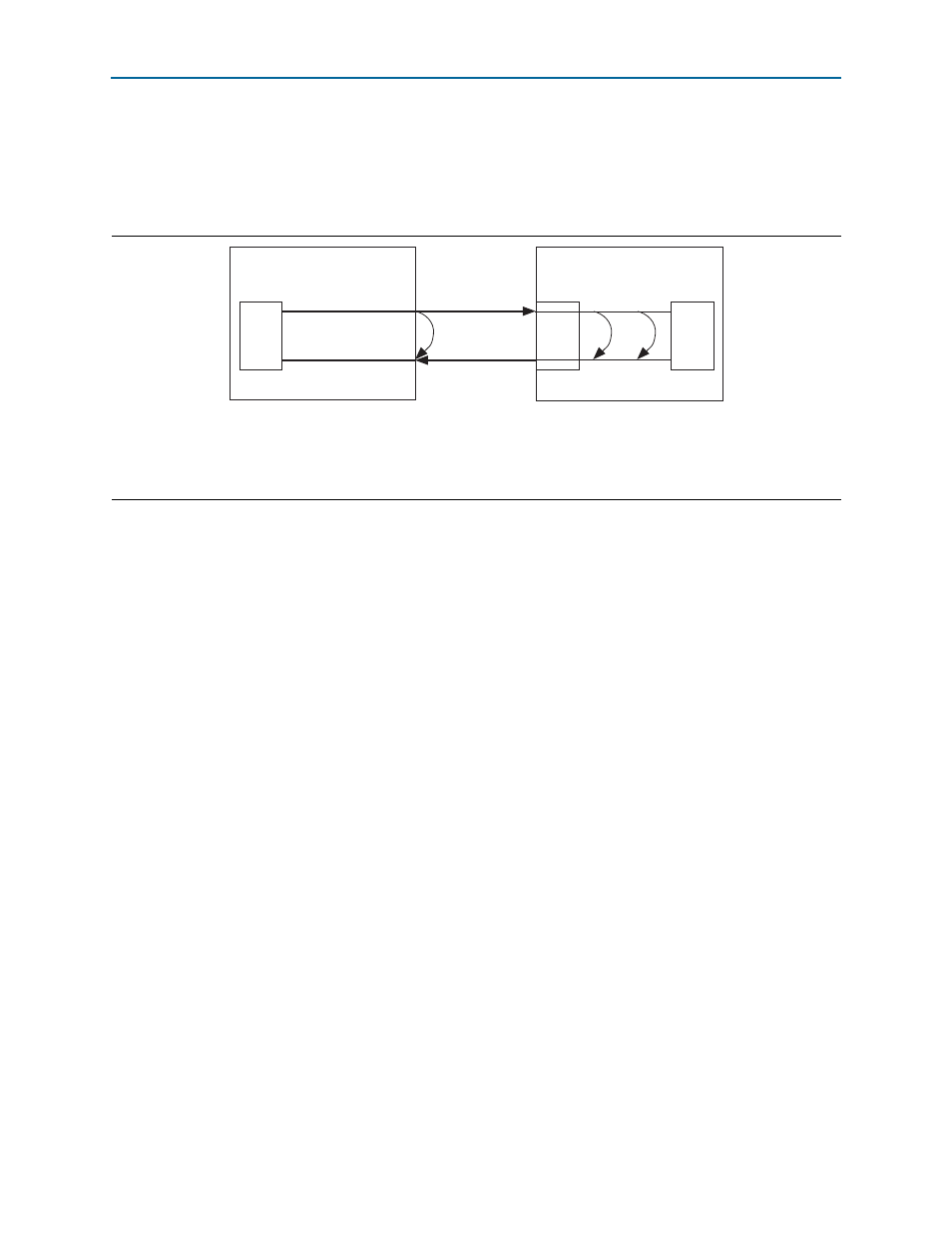

To perform PRBS testing across a CPRI link in external loopback configuration,

connect the CPRI IP core’s high-speed transceiver output to its high-speed transceiver

input, and after the CPU interface is available for programming, perform step

.

shows the three different loopback modes that support PRBS testing.

Achieving Link Synchronization Without an REC Master

Altera provides a self-synchronization testing feature that supports an RE slave in a

CPRI link external loopback configuration. This feature is intended to work correctly

only for Layer 1 testing.

By default, only an REC master can function correctly in a CPRI link external

loopback configuration. An RE slave in external loopback configuration cannot

achieve frame synchronization, because the CPRI Rx interface must lock on to the

K28.5 character before the CPRI Tx interface can begin sending K28.5 characters.

Therefore, no K28.5 character is ever transmitted on the RE slave loopback CPRI link.

However, in an Altera RE slave CPRI IP core, you can specify that the CPRI Tx

interface begin sending K28.5 characters before the CPRI Rx interface locks on to the

K28.5 character from the CPRI link. This feature supports a CPRI RE slave in

achieving frame synchronization without being connected to a CPRI master, and

allows you to test your CPRI RE slave without the need for an additional CPRI IP core

instance.

To use this testing feature in your CPRI RE slave, perform the following steps:

1. Connect your CPRI RE slave in a CPRI link external loopback configuration. (Refer

“External Loopback” on page 5–1

).

2. Ensure that the cleanup PLL drives the

gxb_pll_inclk

input clock to your CPRI

RE slave with a stable signal at the correct frequency, despite the absence of REC

master input to drive the RE slave transceiver CDR and, consequently, the

pll_clkout

output signal of the RE slave. (Refer to

3. Set the

tx_enable_force

bit of the

CPRI_CONFIG

register (

) to

the value of 1. This step activates the self-synchronization testing feature.

Figure 5–2. CPRI IP Core Loopback Modes That Support PRBS Testing

Notes to

(1) External loopback mode to test a single CPRI REC master.

(2) Internal reverse loopback mode (physical layer loopback mode) configured in the RE slave’s

CPRI_PHY_LOOP

register.

(3) Internal reverse loopback mode (testing loopback mode) configured in the RE slave’s

CPRI_CONFIG

register.

RE Slave

REC Master

MAP

Module

CPRI Link

MAP

Module

PHY

Module

(1)

(2)

(3)