Physical layer signals, Cpri data signals, Physical layer signals –12 – Altera CPRI IP Core User Manual

Page 110: Cpri data signals –12

6–12

Chapter 6: Signals

Physical Layer Signals

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

Physical Layer Signals

Table 6–9

through

Table 6–14

list the input and output signals of the physical layer of

the CPRI IP core. Refer to

for details of the I/O signals.

CPRI Data Signals

Table 6–9

lists the CPRI data link signals.

cpu_byteenable[3:0]

Input

CPU data byteenable signal. Enables specific byte lanes during transfers on

ports of width less than 32 bits. Each bit in the

cpu_byteenable

signal

corresponds to a byte lane in

cpu_writedata

and

cpu_readdata

. The least

significant bit of

cpu_byteenable

corresponds to the lowest byte of each

data bus. The bit value 1 indicates an enabled byte lane, and the bit value 0

indicates a disabled byte lane. Enabled byte lanes must be adjacent: valid

values of

cpu_byteenable

include only a single sequence of 1’s.

For more information, refer to the definition of the byteenable signal in the

Avalon-MM specification in the

.

cpu_writedata[31:0]

Input

CPU write data.

cpu_readdata[31:0]

Output

CPU read data.

cpu_waitrequest

Output

Indicates that the CPU interface is busy executing an operation. When this

signal is deasserted, the operation is complete and the data is valid.

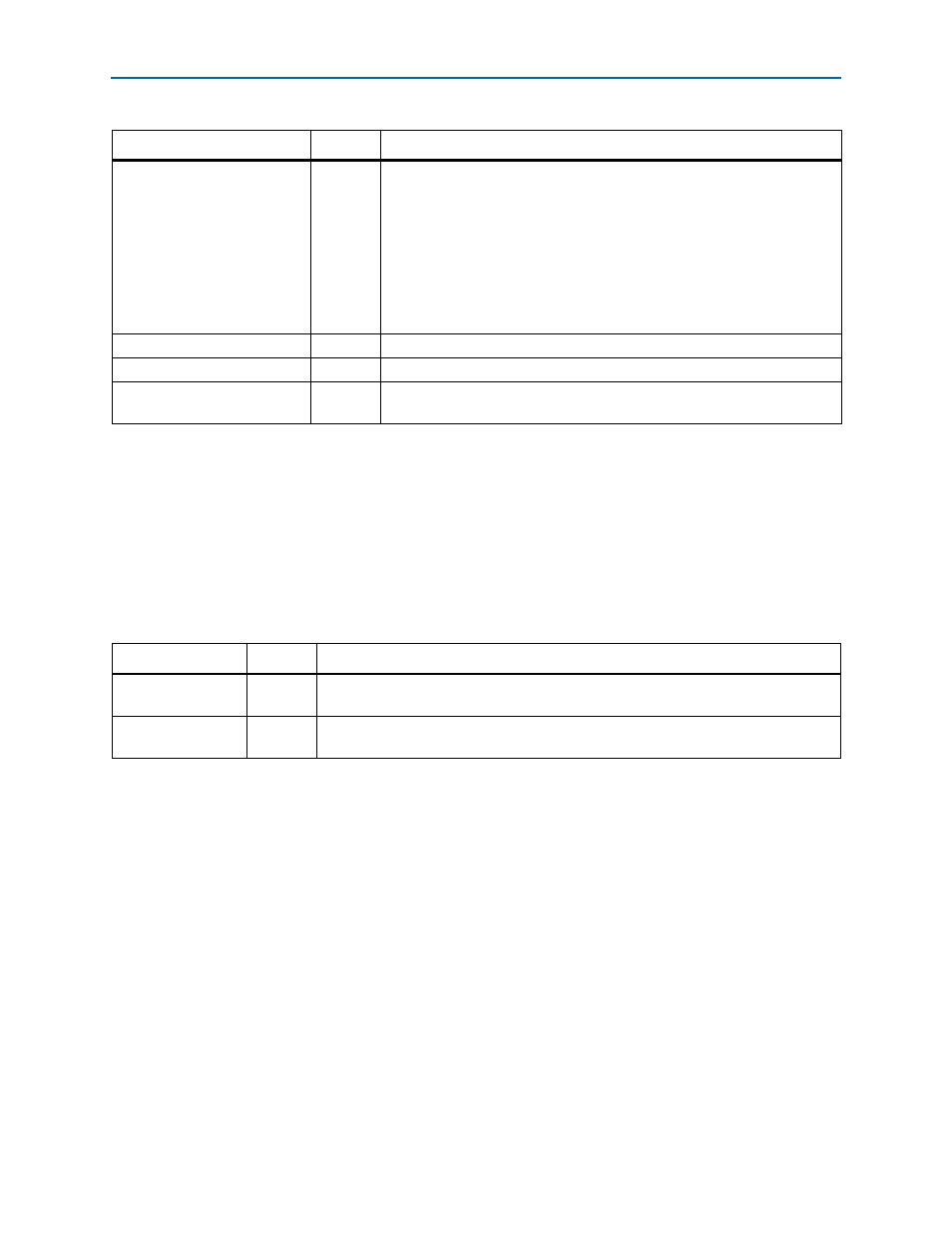

Table 6–8. CPU Interface Signals (Part 2 of 2)

Signal

Direction

Description

Table 6–9. CPRI Protocol Interface

Signal

Direction

Description

gxb_rxdatain

Input

Receive unidirectional serial data. This signal is connected over the CPRI link to the

txdataout

line of the transmitting device.

gxb_txdataout

Output

Transmit unidirectional serial data. This signal is connected over the CPRI link to the

rxdatain

line of the receiving device.