Altera Cyclone II DSP Development Board User Manual

Page 102

Advertising

C–16

Reference Manual

Altera Corporation

Cyclone II DSP Development Board

August 2006

Introduction

GND

K16

N18

GND

GND

K17

N19

GND

GND

K20

N2

CLKIN_TOP

GND

L10

N20

EVM_D4

GND

L12

N21

GND

L13

N22

3.3V

GND

L14

N23

EVM_D31

GND

L15

N24

EVM_DMAC0

GND

L22

N25

CLKIN_BOT

GND

L5

N26

EVM_IACK

GND

M1

N3

EP2C_DATA0

GND

M12

N4

EP2C_CEN

GND

M13

N5

3.3V

GND

M14

N6

EP2C_DCLK

GND

M15

N7

EP2C_CONFIGN

GND

M26

N8

GND

GND

N1

N9

GND

GND

N11

P1

EVM_INUM0

GND

N12

P10

1.2V

GND

N13

P11

GND

GND

N14

P12

GND

GND

N15

P13

GND

GND

N16

P14

GND

GND

N18

P15

GND

GND

N19

P16

GND

GND

N8

P17

1.2V

GND

N9

P18

GND

GND

P11

P19

GND

GND

P12

P2

EVM_CLKOUT2

GND

P13

P20

GND

GND

P14

P21

EP2C_MSEL1

GND

P15

P22

3.3V

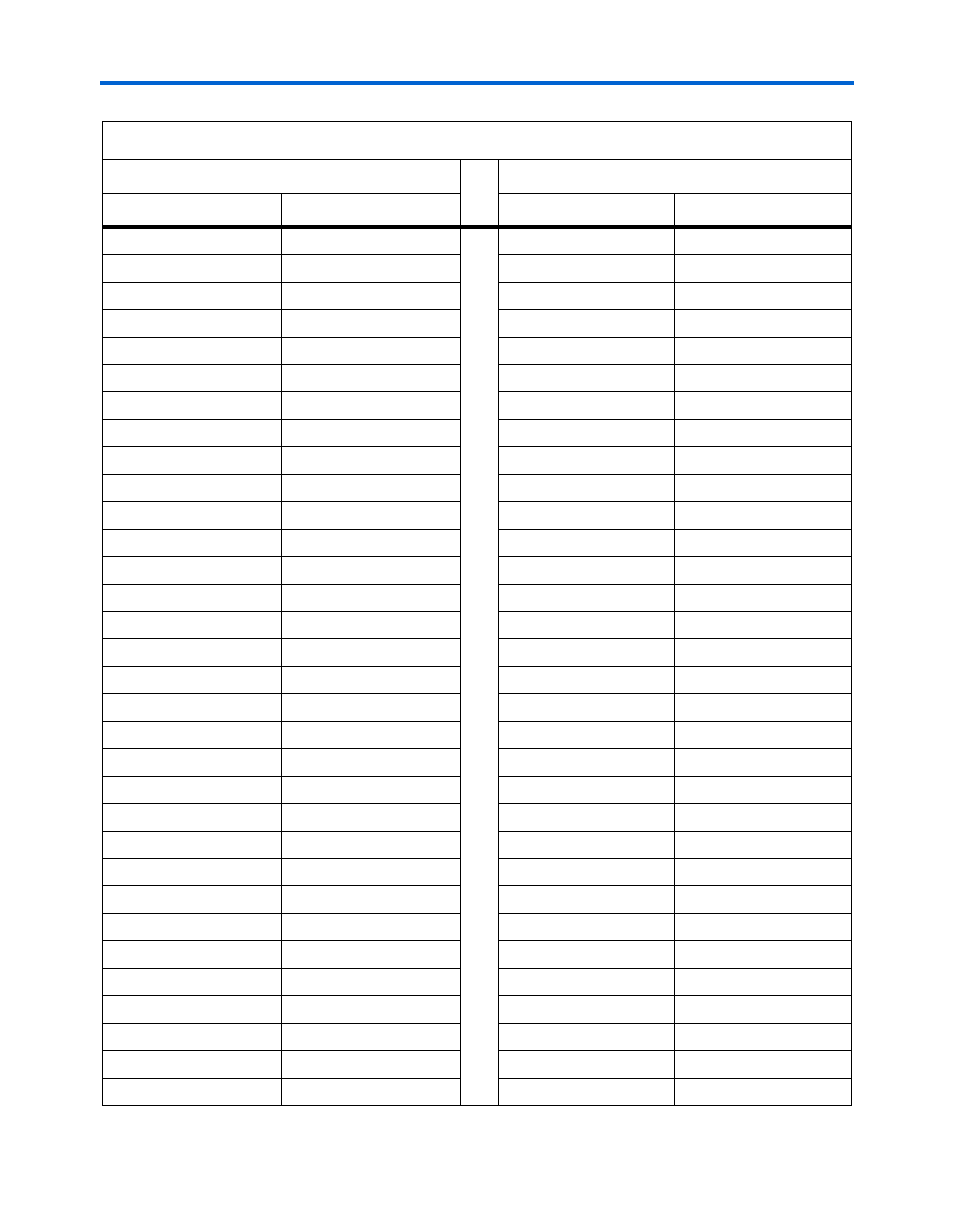

Table C–1. Cyclone II EP2C70F672-C6ES FPGA Pin-Outs (Part 16 of 22)

Note (1)

Alphabetical by Signal Name

Alphabetical by Pin Number

Schematic Signal Name

Pin Number

Pin Number

Schematic Signal Name

Advertising