Altera Cyclone II DSP Development Board User Manual

Page 104

C–18

Reference Manual

Altera Corporation

Cyclone II DSP Development Board

August 2006

Introduction

GND

W14

R5

DAC_A_D12

GND

W19

R6

VGA_G4

GND

W20

R7

VGA_G2

GND

W22

R8

1.2V

GND

W5

R9

3.3V

GND

W7

T1

3.3V

GND

W8

T10

GND

GND

Y17

T11

1.2V

GND

Y9

T12

GND

GND_PLL

AA21

T13

GND

GND_PLL

E21

T14

GND

GND_PLL

E4

T15

GND

GND_PLL

F19

T16

1.2V

GND_PLL

F8

T17

GND

GND_PLL

Y19

T18

1.2V

GND_PLL

Y6

T19

1.2V

GND

Y8

T2

DAC_A_D5

JTAG_CONN_TDI

M7

T20

VGA_R3

JTAG_CONN_TDO

M8

T21

EVM_D23

JTAG_TCK

M6

T22

VGA_R1

JTAG_TMS

L8

T23

DAC_B_D6

PROTO_CARDSELN

V2

T24

ADC_RESET

PROTO_CLKIN

R20

T25

DAC_B_D13

PROTO_CLKOUT

AD13

T26

3.3V

PROTO_IO0

J5

T3

FPGA_TO_ADC_CLK

PROTO_IO1

H6

T4

VGA_CLK

PROTO_IO10

G4

T5

GND

PROTO_IO11

G3

T6

VGA_G6

PROTO_IO12

C2

T7

DIG_MSB_B

PROTO_IO13

F2

T8

1.2V

PROTO_IO14

D1

T9

1.2V

PROTO_IO15

F1

U1

DIG_MSB_F

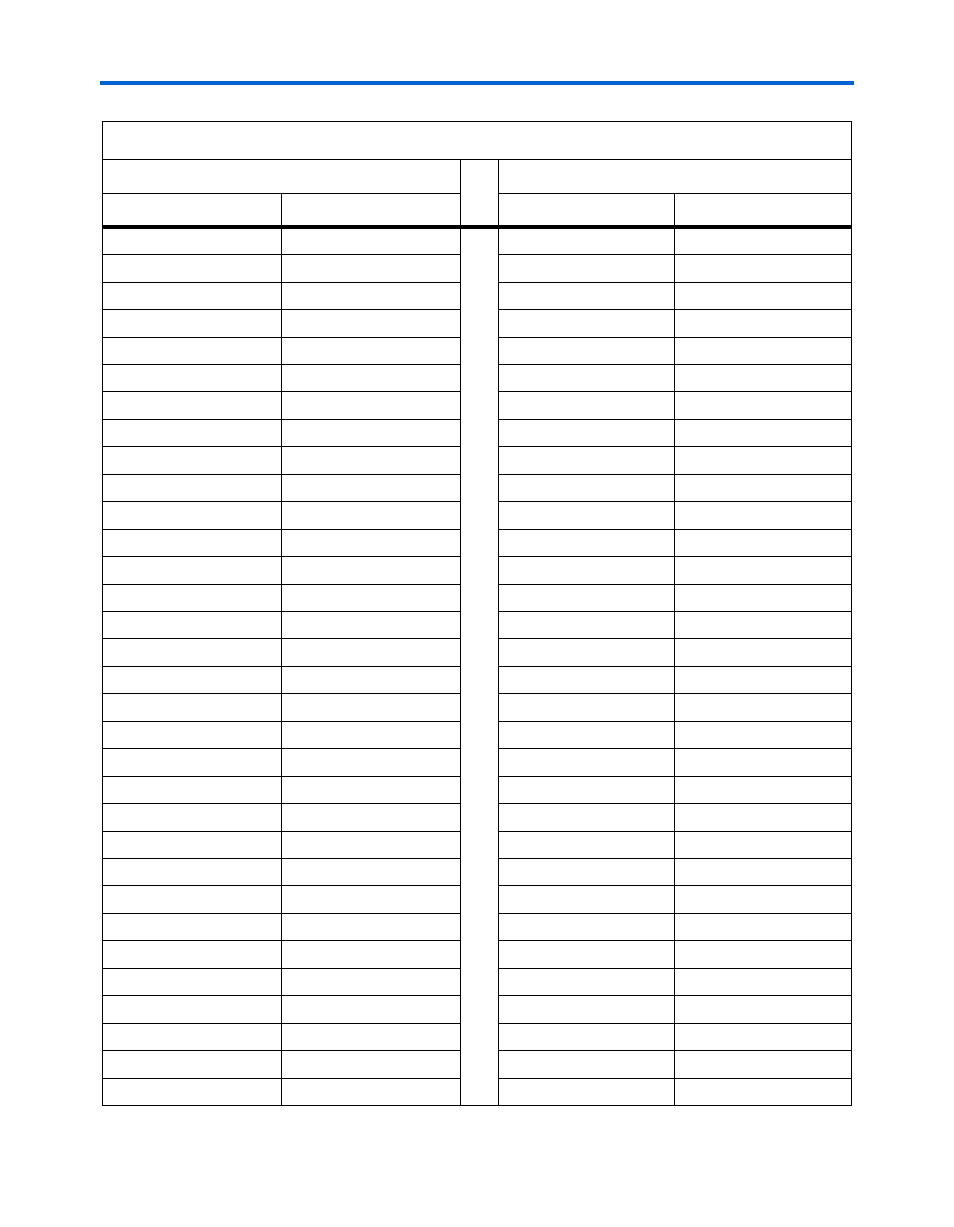

Table C–1. Cyclone II EP2C70F672-C6ES FPGA Pin-Outs (Part 18 of 22)

Note (1)

Alphabetical by Signal Name

Alphabetical by Pin Number

Schematic Signal Name

Pin Number

Pin Number

Schematic Signal Name