Seven-segment display (u32,u33) – Altera Cyclone II DSP Development Board User Manual

Page 21

Altera Corporation

Reference Manual

2–13

August 2006

Cyclone II DSP Development Board

Cyclone II DSP Development Board Components

Seven-Segment Display (U32,U33)

U32 and U33 are dual user defined, seven-segment displays on the

Cyclone II DSP development board. Each segment is individually

controlled by a general purpose I/O pin. When the EP2C70 FPGA pin

drives logic 0, the corresponding segment turns on.

lists the

seven-segment display pin-outs. Figure

shows the name of

each segment.

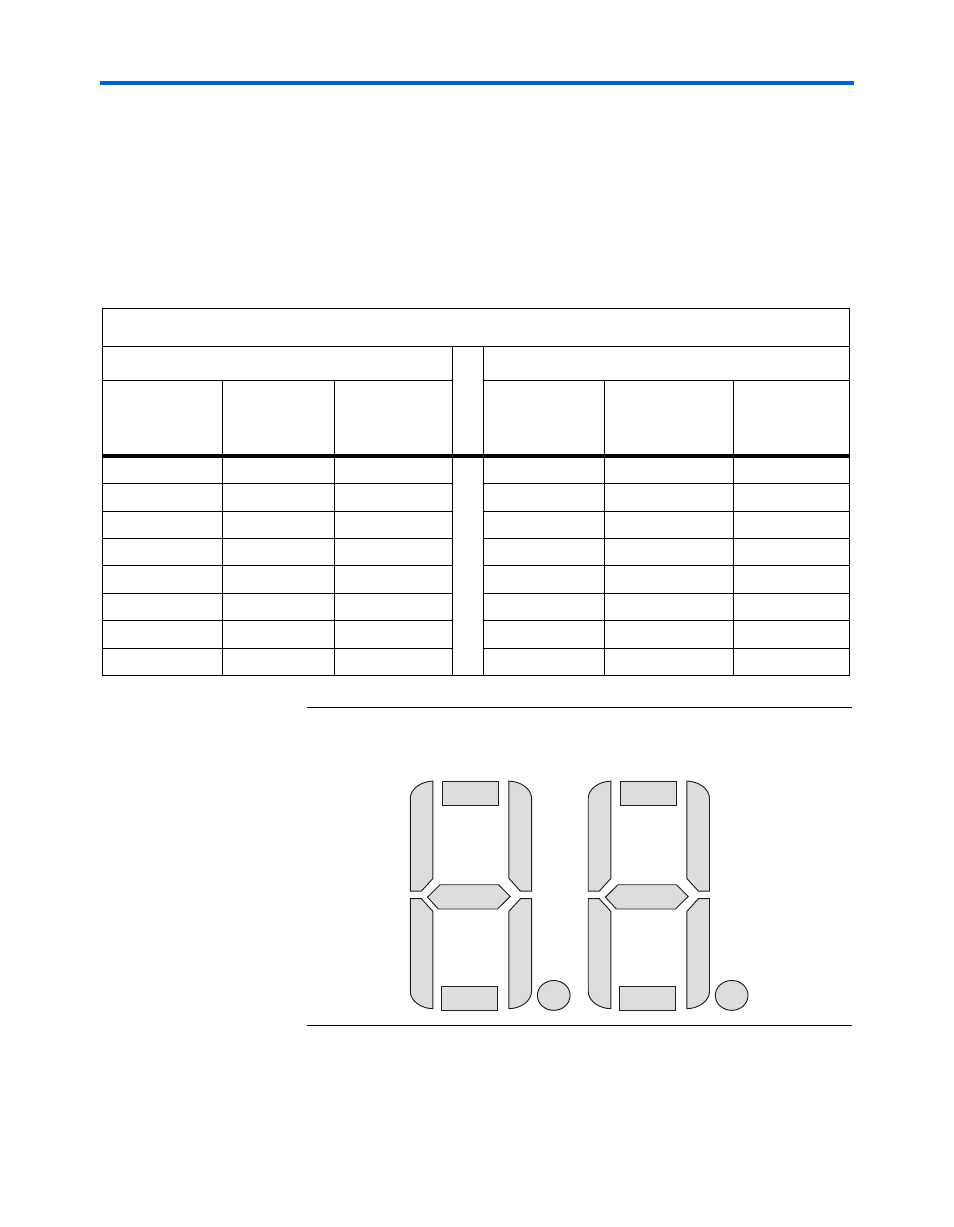

Figure 2–6. Segment Names for the Dual Seven-Segment Displays

Table 2–6. Seven-Segment Display Pin-Outs

U32

U33

Segment

Display Name

Schematic

Signal Name

Cyclone II

(U12) Pin

Name

Segment

Display Name

Schematic

Signal Name

Cyclone II

(U12) Pin

Name

A

DIG_MSB_A

Y21

A

DIG_LSB_A

K2

B

DIG_MSB_B

T7

B

DIG_LSB_B

U25

C

DIG_MSB_C

AB23

C

DIG_LSB_C

AA3

D

DIG_MSB_D

Y5

D

DIG_LSB_D

V1

E

DIG_MSB_E

E1

E

DIG_LSB_E

V7

F

DIG_MSB_F

U1

F

DIG_LSB_F

U23

G

DIG_MSB_G

W21

G

DIG_LSB_G

AC2

DP

DIG_MSB_DP

V3

DP

DIG_LSB_DP

P7

DP

G

D

A

C

E

B

F

U32

DP

G

D

A

C

E

B

F

U33