Figure 2–12, Show – Altera Cyclone II DSP Development Board User Manual

Page 36

Advertising

2–28

Reference Manual

Altera Corporation

Cyclone II DSP Development Board

August 2006

Memory Components

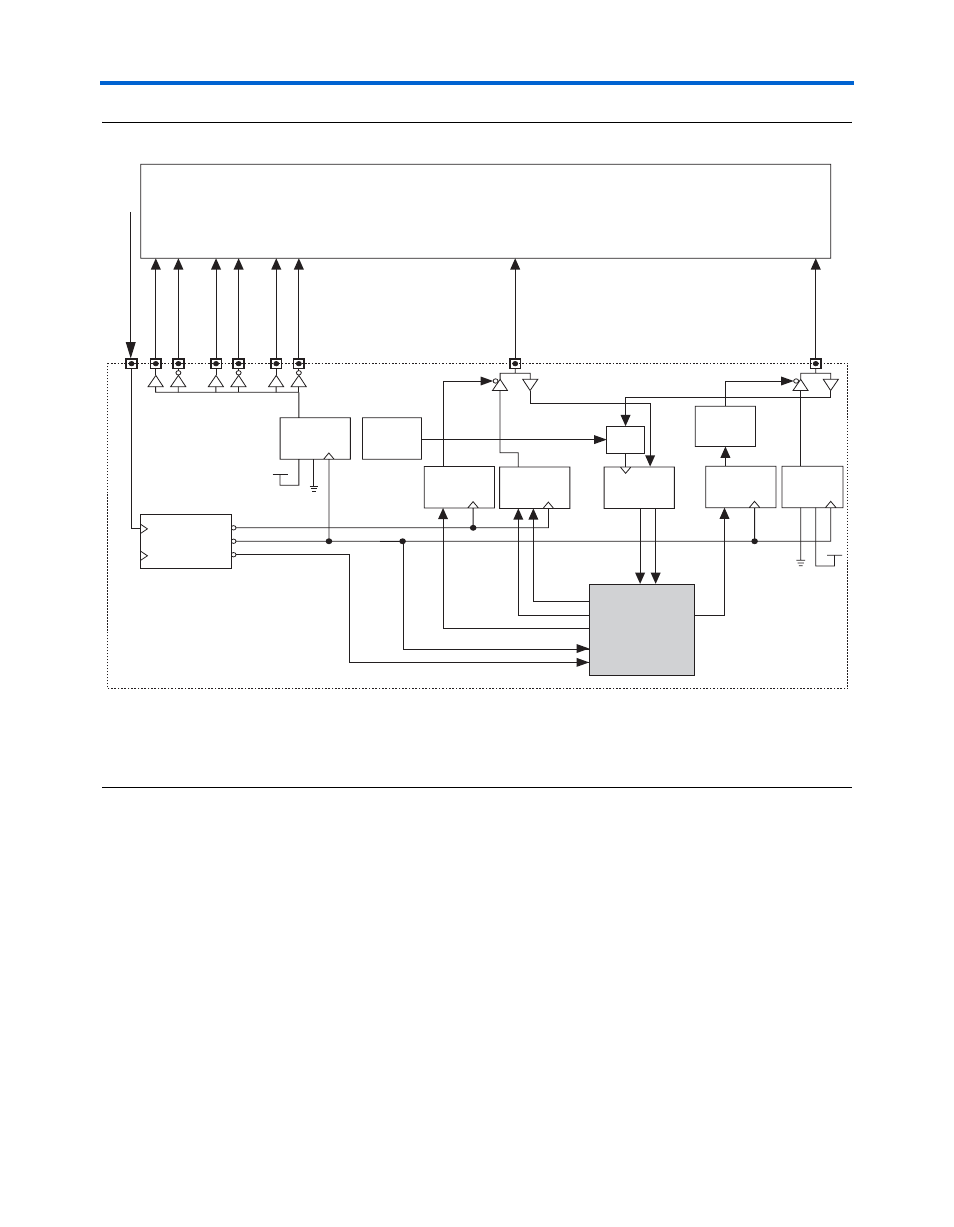

Figure 2–12. DDR2 SDRAM DIMM Clocking Diagram

Note to

(1)

One DDR register consists of one I/O register, one core register, and one output multiplexer.

(2)

See

Figure 2–21, "Cyclone II DSP Development Board Clocking Options"

for timing source inforamtion.

DDR Out

Reg

O E Out

Reg

DDR Out

Reg

O E Out

Reg

DDR Out

Reg

DDR In

Reg

Preamble

control

Delay

Delay

control

Non-I/O-Related

Logic

EP2C35F672 FPGA

DIMM_CK_P0

DIMM_CK_P1

DIMM_CK_P2

DIMM_CK_N1

DIMM_CK_N0

DIMM_CK_N2

DIMM_DQ(71:0)

DIMM_DQS(8:0)

DDR2 SDRAM DIMM

-90˚ shift

0˚ shift

2ns˚ shift

DQS In

DQS Out

delay_val

PLL

IN 0

Timin

g

Source

(2

)

IN 1

G0

G1

G2

CLKIN_T

OP or CLKIN_BO

T

2

Advertising