Altera Cyclone II DSP Development Board User Manual

Page 89

Altera Corporation

Reference Manual

C–3

August 2006

Cyclone II DSP Development Board

1.2V

W17

AB16

GND

1.2V

Y20

AB17

1.8V

1.2V

Y7

AB18

DIMM_CSN_R1

1.8V

A11

AB19

GND

1.8V

A16

AB2

AUDIO_LRCOUT

1.8V

A24

AB20

DIMM_CK_P1

1.8V

A3

AB21

DIMM_SYNC_CLK

1.8V

AB13

AB22

1.8V

1.8V

AB14

AB23

DIG_MSB_C

1.8V

AB17

AB24

EVM_D29

1.8V

AB22

AB25

EVM_D1

1.8V

AB6

AB26

EVM_D3

1.8V

AB9

AB3

AUDIO_CLK

1.8V

AD20

AB4

USER_LED5

1.8V

AF11

AB5

3.3V

1.8V

AF16

AB6

1.8V

1.8V

AF24

AB7

GND

1.8V

AF3

AB8

DIMM_A_R7

1.8V

C20

AB9

1.8V

1.8V

D22

AC1

VGA_B0

1.8V

E13

AC10

VREF

1.8V

E14

AC11

DIMM_DQ16

1.8V

E17

AC12

VREF

1.8V

E6

AC13

USER_DIPSW0

1.8V

E9

AC14

DIMM_DQ10

1.8V

H18

AC15

DIMM_DM0

1.8V

H9

AC16

VREF

1.8V

J12

AC17

DIMM_DQ1

1.8V

J15

AC18

USER_PB0

1.8V

V12

AC19

DIMM_CKE_R1

1.8V

V15

AC2

DIG_LSB_G

1.8V

W18

AC20

USER_DIPSW5

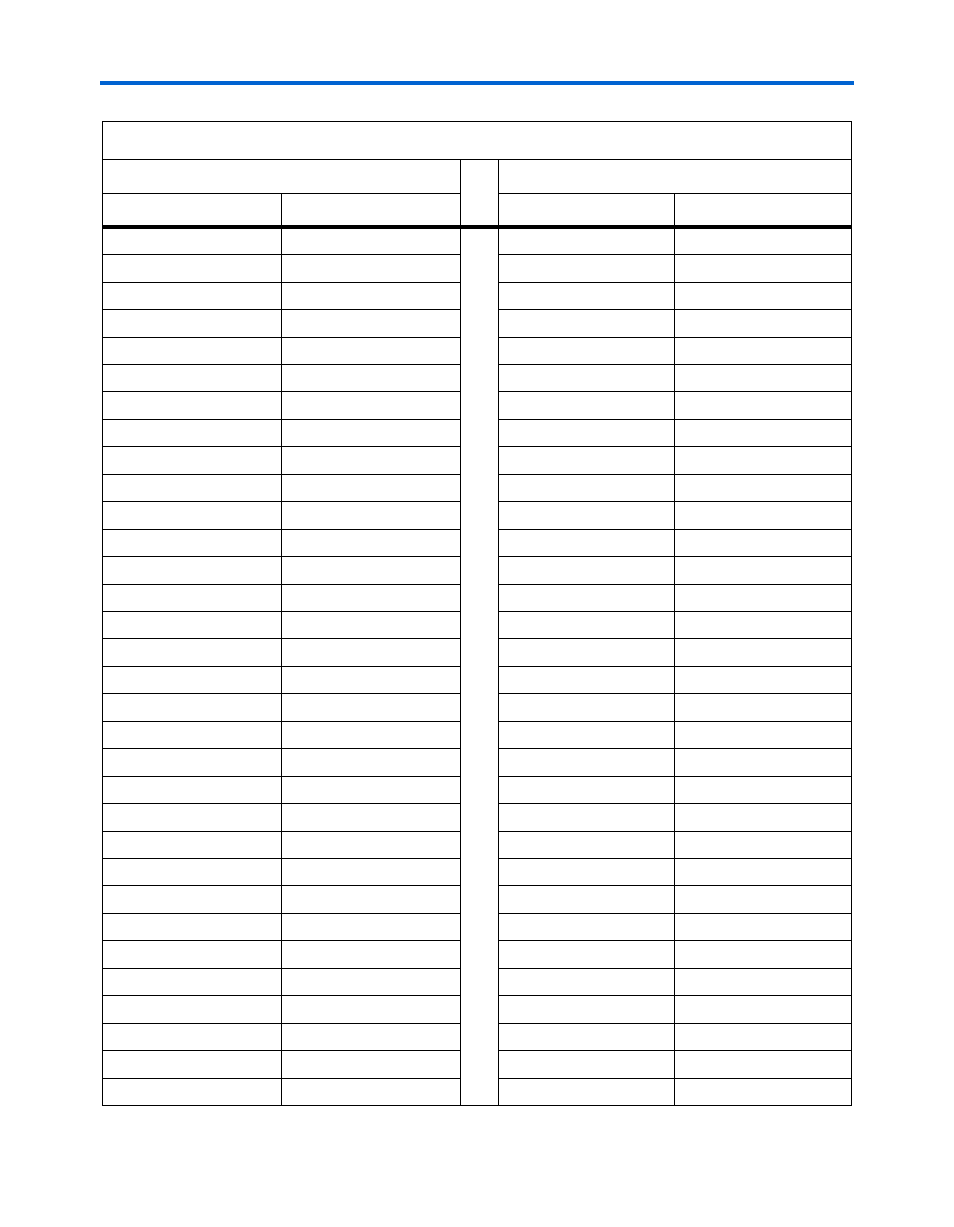

Table C–1. Cyclone II EP2C70F672-C6ES FPGA Pin-Outs (Part 3 of 22)

Note (1)

Alphabetical by Signal Name

Alphabetical by Pin Number

Schematic Signal Name

Pin Number

Pin Number

Schematic Signal Name