Altera Cyclone II DSP Development Board User Manual

Page 91

Altera Corporation

Reference Manual

C–5

August 2006

Cyclone II DSP Development Board

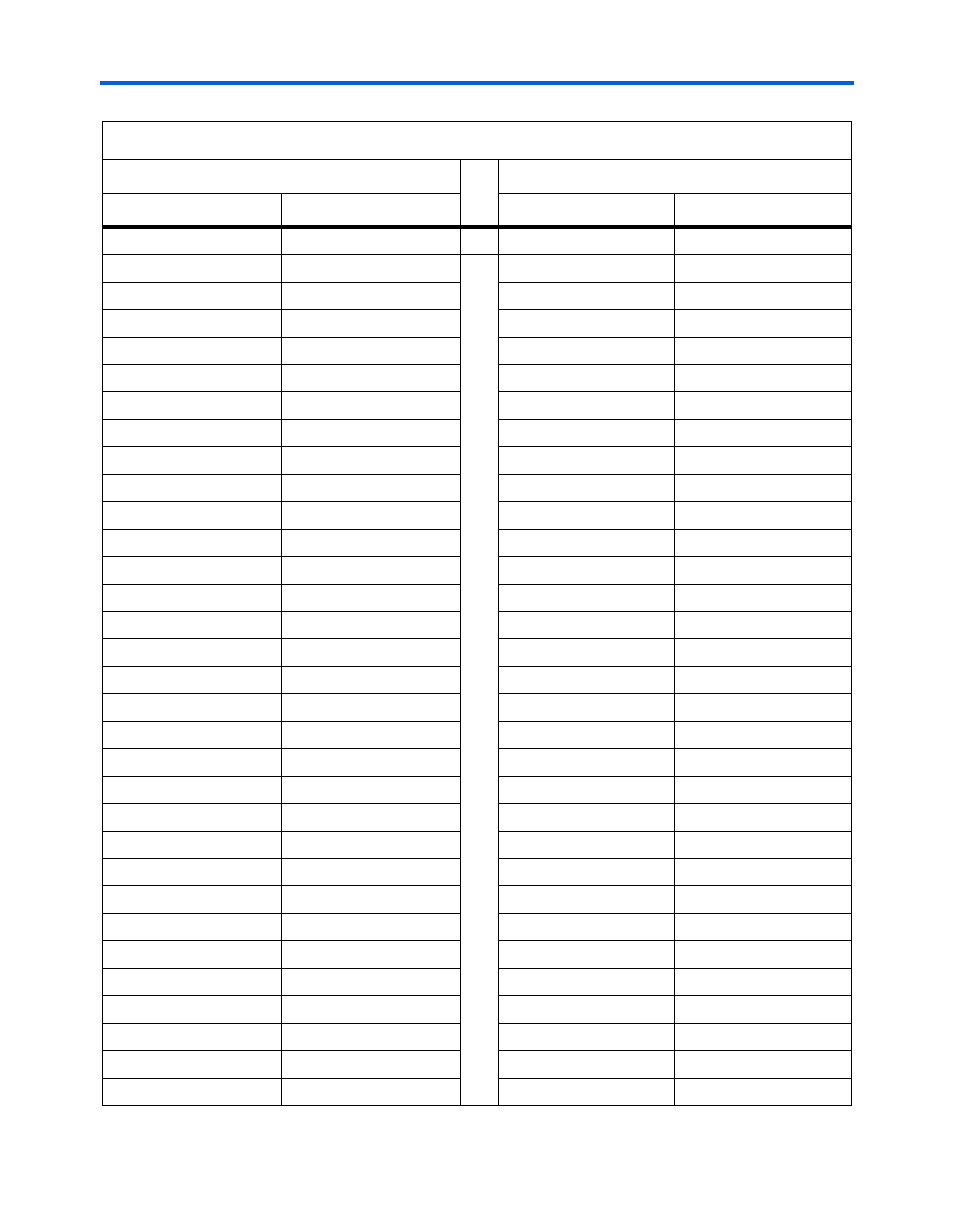

ADC_A_D4

A9

AD3

DAC_A_D3

ADC_A_D5

C11

AD4

DIMM_A_R11

ADC_A_D6

B12

AD5

DIMM_A_R8

ADC_A_D7

D13

AD6

DIMM_A_R2

ADC_A_D8

B22

AD7

DIMM_A_R5

ADC_A_D9

A21

AD8

DIMM_DM3

ADC_A_DCLK

A13

AD9

GND

ADC_A_OE

F7

AE1

GND

ADC_A_OVR

D15

AE10

DIMM_DQ18

ADC_A_SEN

B18

AE11

DIMM_A_R9

ADC_B_D0

F17

AE12

DIMM_DQ15

ADC_B_D1

D17

AE13

DIMM_DQS2

ADC_B_D10

E18

AE14

USER_PB3

ADC_B_D11

E20

AE15

DIMM_DQS1

ADC_B_D12

D21

AE16

USER_PB1

ADC_B_D13

D20

AE17

DIMM_DQ2

ADC_B_D2

D18

AE18

USER_DIPSW6

ADC_B_D3

C19

AE19

USER_DIPSW7

ADC_B_D4

B19

AE2

VGA_SYNCN

ADC_B_D5

B20

AE20

DIMM_RASN_R

ADC_B_D6

A20

AE21

DIMM_CKE_R0

ADC_B_D7

B21

AE22

USER_PB2

ADC_B_D8

F18

AE23

DIMM_ODT_R1

ADC_B_D9

G18

AE24

ADC_B_DCLK

C13

AE25

EVM_CEN3

ADC_B_OE

R2

AE26

GND

ADC_B_OVR

A6

AE3

DAC_A_D2

ADC_B_SEN

D19

AE4

DIMM_A_R0

ADC_RESET

T24

AE5

DIMM_A_R10

ADC_SCLK

AD24

AE6

DIMM_DQ26

ADC_SDATA

Y1

AE7

DIMM_DQ27

AUDIO_BCLK

F3

AE8

DIMM_DQS3

Table C–1. Cyclone II EP2C70F672-C6ES FPGA Pin-Outs (Part 5 of 22)

Note (1)

Alphabetical by Signal Name

Alphabetical by Pin Number

Schematic Signal Name

Pin Number

Pin Number

Schematic Signal Name