Signals, Physical layer signals, Chapter 5. signals – Altera RapidIO MegaCore Function User Manual

Page 115: Physical layer signals –1, Chapter 5, signals, Chapter 5

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

5. Signals

This chapter lists the RapidIO IP core signals.

Qsys allows you to export signals with different names or prefixes. Refer to the Qsys

System Contents

tab for the signals that support this capability individually, and to

the Qsys HDL Example tab for the list of signals that are bundled together as

exported_connections

. The signals bundled in exported_connections all take the

prefix you specify in the Qsys System Contents tab.

A yes entry in the Exported by Qsys column in the following tables indicates that the

signal is included in the exported_connections conduit in Qsys. A no entry indicates

that the signal is not included in the exported_connections conduit in Qsys.

Physical Layer Signals

through

Table 5–10

list the pins used by the Physical layer of the RapidIO IP

core. Refer to

for details of the I/O signals.

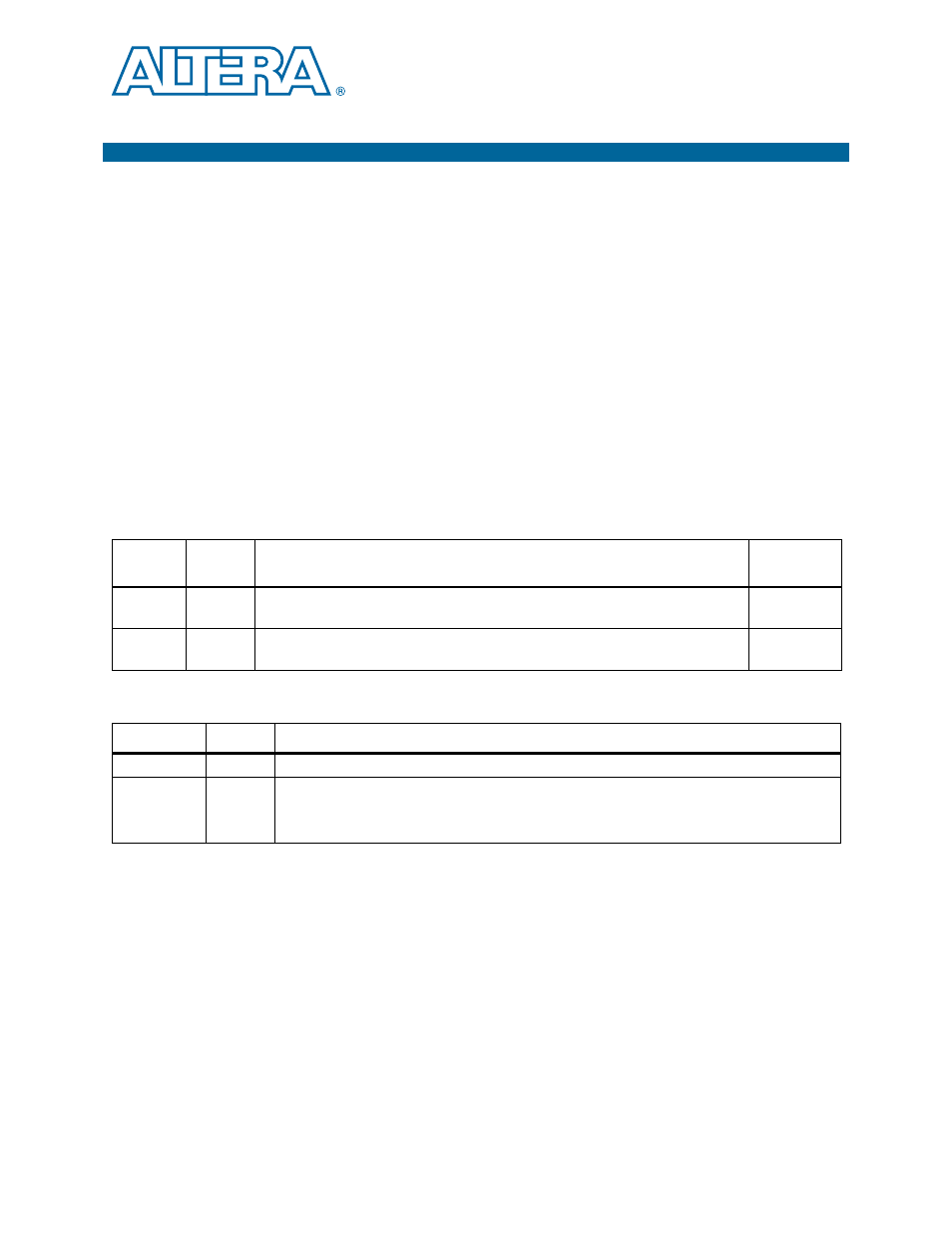

Table 5–1. RapidIO Interface

Signal

Direction

Description

Exported by

Qsys

rd

Input

Receive data—a unidirectional data receiver. It is connected to the td bus of the

transmitting device.

yes

td

Output

Transmit data—a unidirectional data driver. The td bus of one device is connected

to the rd bus of the receiving device.

yes

Table 5–2. Main Clock Signals

Signal

Direction

Description

sysclk

Input

Avalon system clock

clk

Input

Physical layer reference clock.

In Arria 10 variations, this clock is the reference clock for the RX CDR block in the transceiver.

In other variations, this clock is also the reference clock for the TX PLL in the transceiver.

Note to

Table 5–2

:

(1) You must ensure that you drive this clock from a clock source that is running reliably when the RapidIO IP core comes out of reset.