Maintenance register, Maintenance slave processor, Figure 4–12 – Altera RapidIO MegaCore Function User Manual

Page 74

4–28

Chapter 4: Functional Description

Logical Layer Modules

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

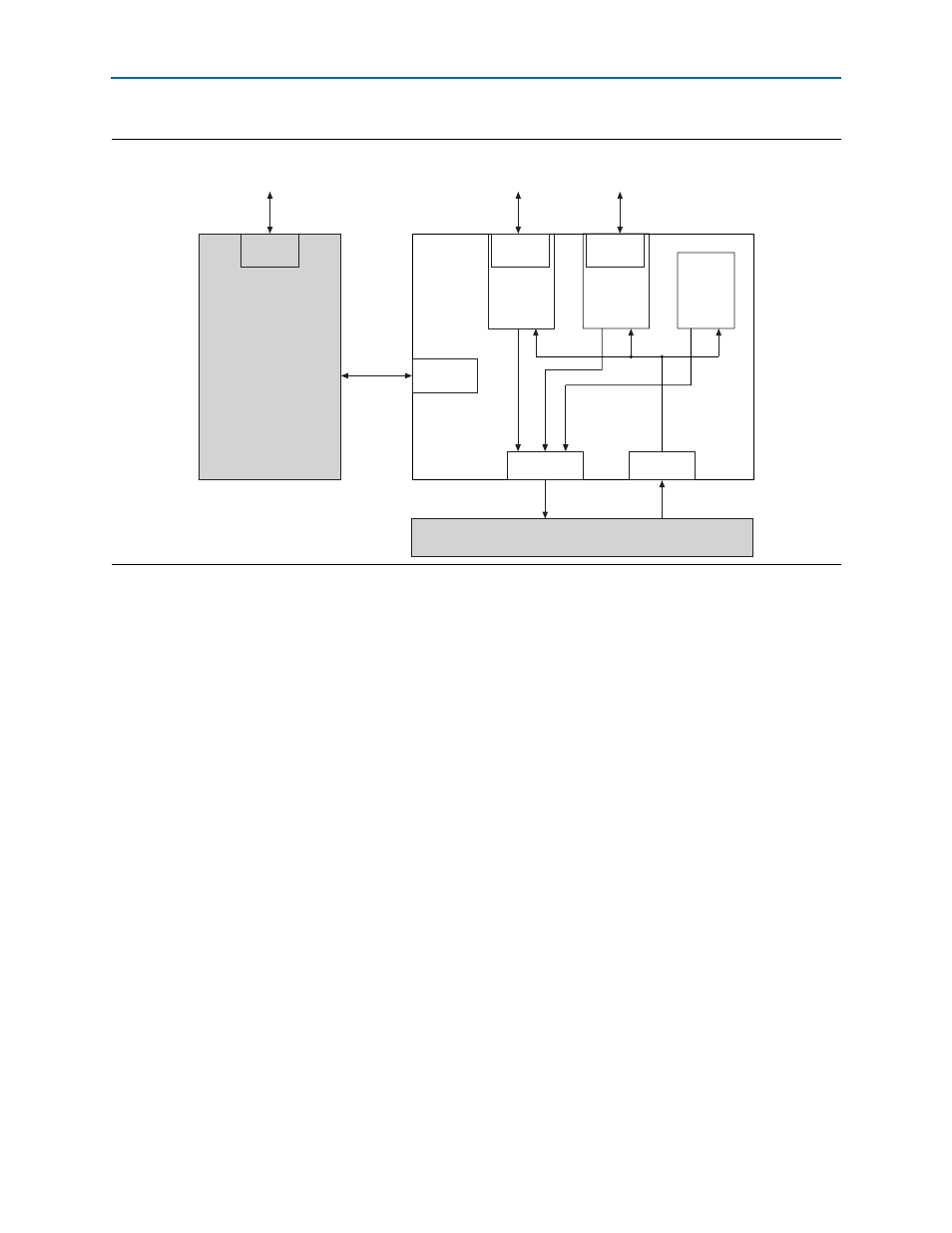

Maintenance Register

The Maintenance Register module implements all of the control and status registers

required by this module to perform its functions. These include registers described in

. These registers are

accessible through the System Maintenance Avalon-MM interface.

Maintenance Slave Processor

The Maintenance Slave Processor module performs the following tasks:

■

For an Avalon read, composes the RapidIO logical header fields of a MAINTENANCE

read request packet

■

For an Avalon write, composes the RapidIO logical header fields of a MAINTENANCE

write request packet

■

Maintains status related to the composed MAINTENANCE packet

■

Presents the composed MAINTENANCE packet to the Transport layer for transmission

The Avalon-MM slave interface allows you to initiate a MAINTENANCE read or write

operation. The Avalon-MM slave interface supports the following Avalon transfers:

■

Single slave write transfer with variable wait-states

■

Pipelined read transfers with variable latency

1

At any time, there can be a maximum of 64 outstanding MAINTENANCE requests that can

be MAINTENANCE reads, MAINTENANCE writes, or port-write requests.

f

Refer to the

for more details on the supported transfers.

Figure 4–12. Maintenance Module Block Diagram

Transport Layer

maintenance

register

Register

Interface

Concentrator

System Maintenance

Avalon-MM Slave Interface

slave

processor

master

processor

port_write

processor

Avalon-MM

Slave

Avalon-MM

Slave

Avalon-MM

Master

Tx Interface

Rx Interface

Maintenance

Avalon-MM Slave

Interface

Maintenance

Avalon-MM Master

Interface