Figure 4–10 – Altera RapidIO MegaCore Function User Manual

Page 71

Chapter 4: Functional Description

4–25

Logical Layer Modules

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

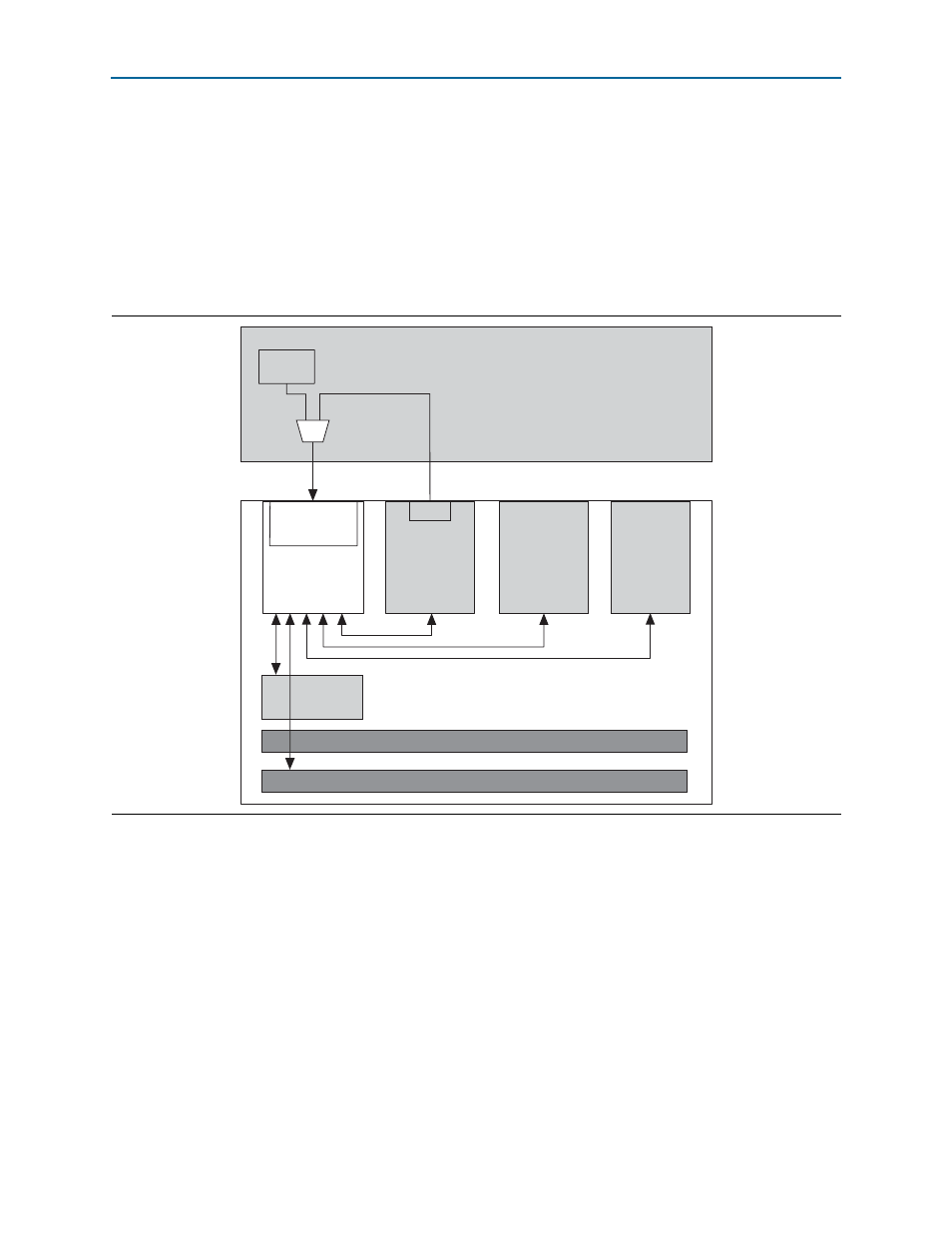

A local host can access the RapidIO registers from a Qsys system as illustrated in

. In this figure, a Nios II processor is part of the Qsys system and is

configured as an Avalon-MM master that accesses the RapidIO IP core registers

through the System Maintenance Avalon-MM slave. Alternatively, you can

implement custom logic to access the RapidIO registers as shown in

f

For implementation details, refer to the System Design with Qsys section in

of

the Quartus II Handbook.

Figure 4–10. Local Host Accesses RapidIO Registers from a Qsys System

Maintenance

Master

CARs

and

CSRs

Nios II

Processor

System Interconnect

Qsys System

I/O Master

I/O Slave

Concentrator

System

Maintenance

Avalon-MM Slave

Transport Layer

Physical Layer

Transport Layer