Altera RapidIO MegaCore Function User Manual

Page 171

Chapter 7: Testbenches

7–9

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

(refer to

). It programs the payload to be incrementing,

starting at 0x0C01, and the DESTINATION_ID to have value 0xAA or 0xAAAA, matching

the device ID of the DUT.

The test waits for the DUT to assert the drbell_s_irq signal, which indicates that a

DOORBELL

message has been received. The test then reads the eight received DOORBELL

messages, by calling the rw_data task with a ‘READ operation to the Rx DOORBELL

register at offset 0x0000_0000. The task is called eight times, once for each message. It

returns the received DOORBELL message and the message is checked for an

incrementing payload starting at 0x0C01 and for the sourceId value 0x55 or 0x5555,

the device ID of the sister RapidIO IP core variation.

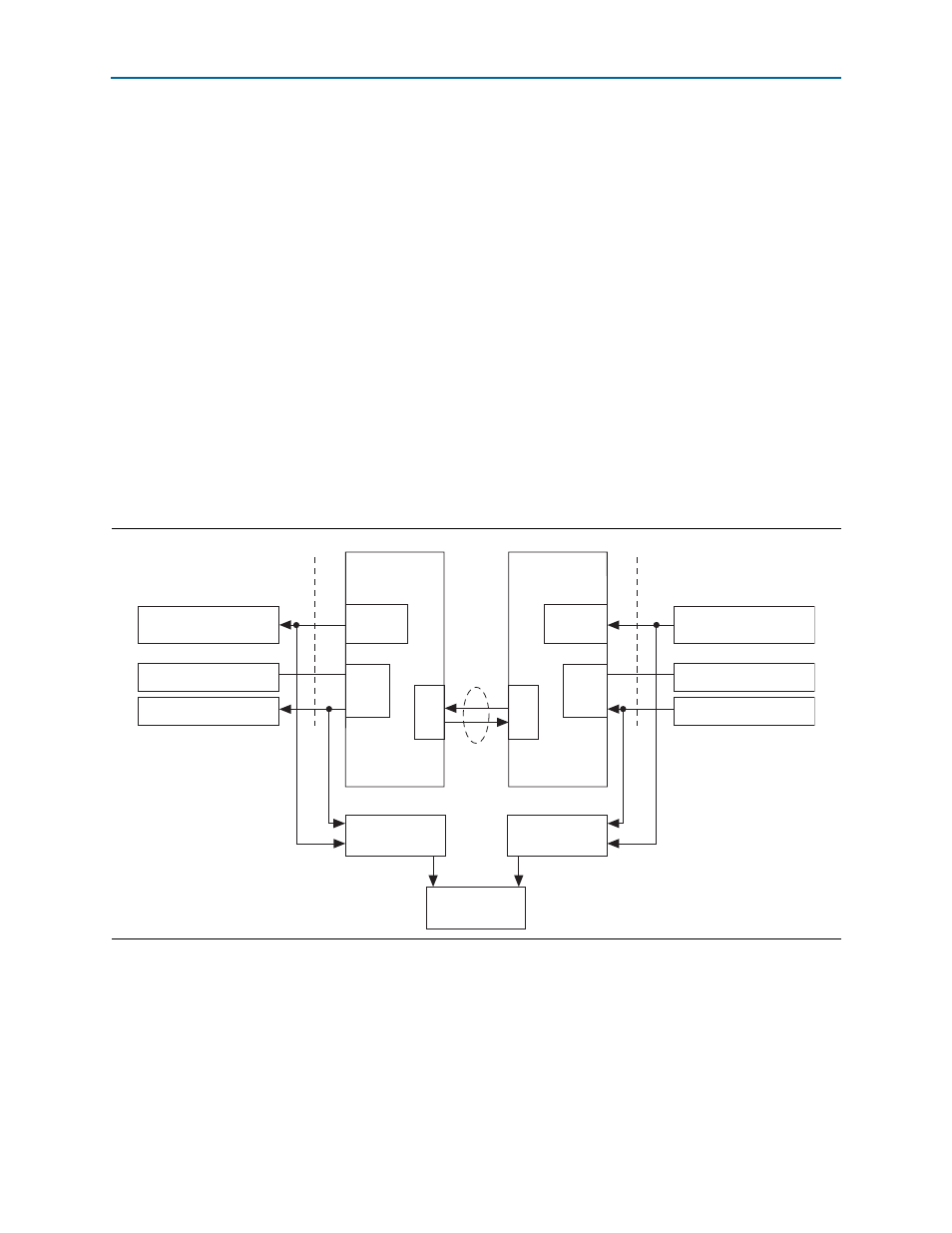

Doorbell and Write Transactions With Transaction Order Preservation

shows the testbench for checking transaction order preservation. The test

generates write transactions and Doorbell messages, and compares the transaction

order before and after the transactions are transmitted on the RapidIO link. If a

Doorbell module and I/O slave port are instantiated in the DUT, and in non-Arria 10

variations Prevent doorbell messages from passing write transactions is turned on

in the RapidIO parameter editor, the extra hardware is generated in the testbench.

The transaction ordering test has two parts. The first part checks that transaction

order is preserved among I/O write requests and Doorbell messages. The second part

injects errors in the write transactions to force transaction cancellation, to test the

integrity of the COMPLETED_OR_CANCELLED_WRITES field of the Input/Output Slave

RapidIO Write Requests

register. Because the behavior of the write transactions

themselves is not under test, but only the preservation of transaction ordering

between Doorbell messages and write requests, each part of the transaction ordering

test generates only one type of write transaction.

Figure 7–2. Transaction Order Preservation Testbench

PHY

PHY

Avalon-MM

sister_rio

Serial

RapidIO

Interface

Avalon-MM

DUT

I/O

Slave

bfm_io_read_master

bfm_io_write_master

sister_bfm_io_read_master

sister_bfm_io_write_master

I/O

Slave

sister_bfm_drbell_master

Doorbell

Slave

Doorbell

Slave

bfm_drbell_master

Receive Queue

Transmit Queue

Comparator