Altera RapidIO MegaCore Function User Manual

Page 70

4–24

Chapter 4: Functional Description

Logical Layer Modules

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

1

Registers in the Doorbell Logical layer module are not accessed through the

Concentrator. Instead, they are accessed directly through the Doorbell module's

Avalon-MM slave interface.

The Concentrator module provides access to the Avalon-MM slave interface and the

RapidIO IP core register set. The interface supports simple reads and writes with

variable latency. Accesses are to 32-bit words addressed by a 17-bit wide byte address.

When accessed, the lower 2 bits of the address are ignored and assumed to be 0, which

aligns the transactions to 4-byte words. The interface supports an interrupt line,

sys_mnt_s_irq

. When enabled, the following interrupts assert the sys_mnt_s_irq

signal:

■

Received port-write

■

I/O read out of bounds

■

I/O write out of bounds

■

Invalid write

■

Invalid write burstcount

For details on these and other interrupts, refer to

show different ways to access the RapidIO registers.

A local host can access these registers using one of the following methods:

■

Qsys interconnect

■

Custom logic

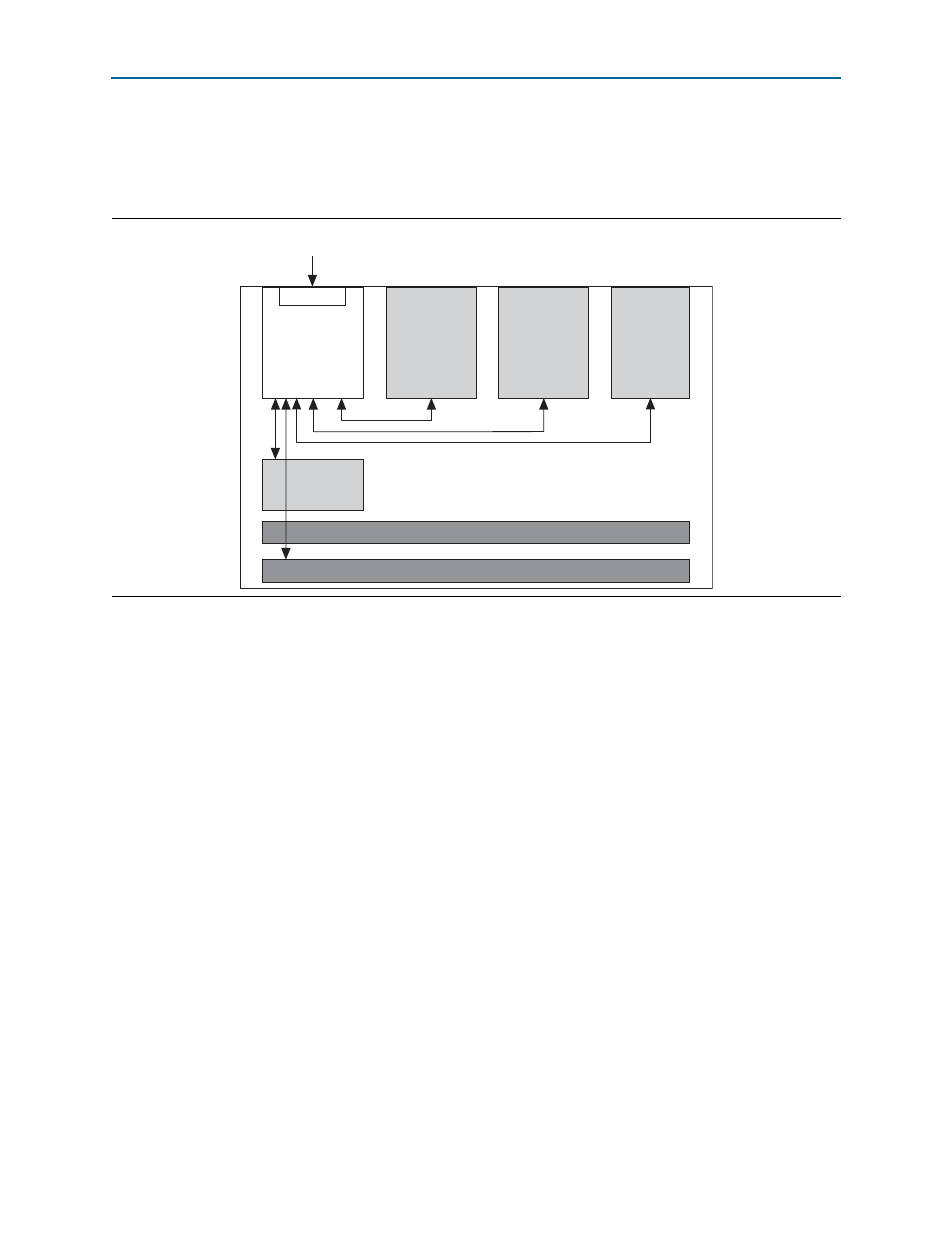

Figure 4–9. Concentrator Module Provides Configuration Register Access

CARs

and

CSRs

I/O Master

I/O Slave

Concentrator

Transport Layer

Physical Layer

Transport Layer

Maintenance

Avalon Slave

System Maintenance

Avalon-MM Slave