Connecting unconnected clocks, Connecting system components – Altera RapidIO MegaCore Function User Manual

Page 183

Chapter 8: Qsys Design Example

8–9

Running Qsys

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

Connecting Unconnected Clocks

Information about the clocks in the system appears in the Connections, Name,

Description

, and Clock columns.

Connect all clocks designated as unconnected in the Clock column. Click unconnected

in the Clock column to assign the clock to clk_0.

This instruction does not affect the rapidio_0.clk port, which you exported

previously. This port is designated exported in the Clock column.

1

You must ensure that you also connect the calibration clock (cal_blk_clk) to a clock

with the appropriate frequency range 10–125 MHz. In this example, the default

external clock, clk_0, is in this range.

Connecting System Components

In Qsys, clicking and hovering the mouse over the Connections column displays the

potential connection points between components, represented as dots connecting

wires. A filled dot shows that a connection is made; an open dot shows a potential

connection point that is not currently connected. Clicking a dot toggles the connection

status. To complete this design, create the connections listed in

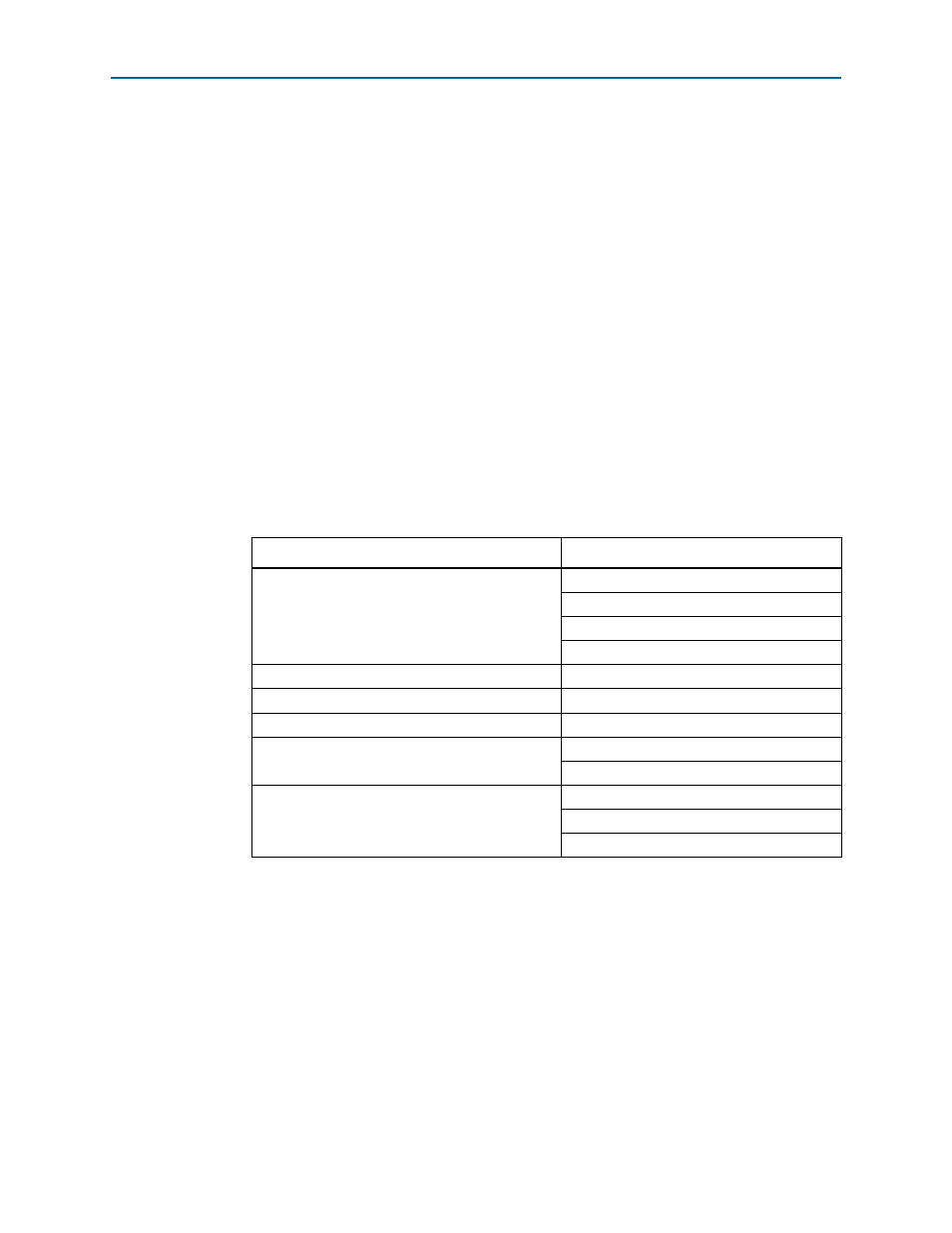

Table 8–6. Connect System Components

Make Connection From

To

clk_0 clk_reset

rapidio_0 clock_reset

master_bfm clk_reset

master_bfm_io clk_reset

onchip_mem... reset1

rapidio_0 mnt_master

rapidio_0 sys_mnt_slave

rapidio_0 io_read_master

onchip_mem... s1

rapidio_0 io_write_master

onchip_mem... s1

master_bfm m0

rapidio_0 mnt_slave

rapidio_0 sys_mnt_slave

master_bfm_io m0

rapidio_0 io_write_slave

rapidio_0 io_read_slave

onchip_mem... s1