Altera RapidIO MegaCore Function User Manual

Page 15

Chapter 1: About This MegaCore Function

1–7

Performance and Resource Utilization

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

■

Maintenance master and slave

to

list the resources and expected performance for selected

variations that use these modules:

■

Physical layer with 8 KByte transmit buffers and 4 KByte receive buffers

■

Transport layer

■

Input/Output Avalon-MM master and slave

The numbers of LEs, combinational ALUTs, ALMs, and primary logic registers are

rounded up to the nearest 100.

shows results obtained using the Quartus II software v14.0 Arria 10 Edition

for an Arria 10 10AX115S1F45E1LP device.

shows results obtained using the Quartus II software v13.0 for the following

devices:

■

Arria V GX (5AGXBB1D4F31C4)

■

Arria V GZ (5AGZME1H2F35C3)

■

Cyclone V (5CGXFC7C6F23C6)

■

Stratix V (5SGXMA7H2F35C2)

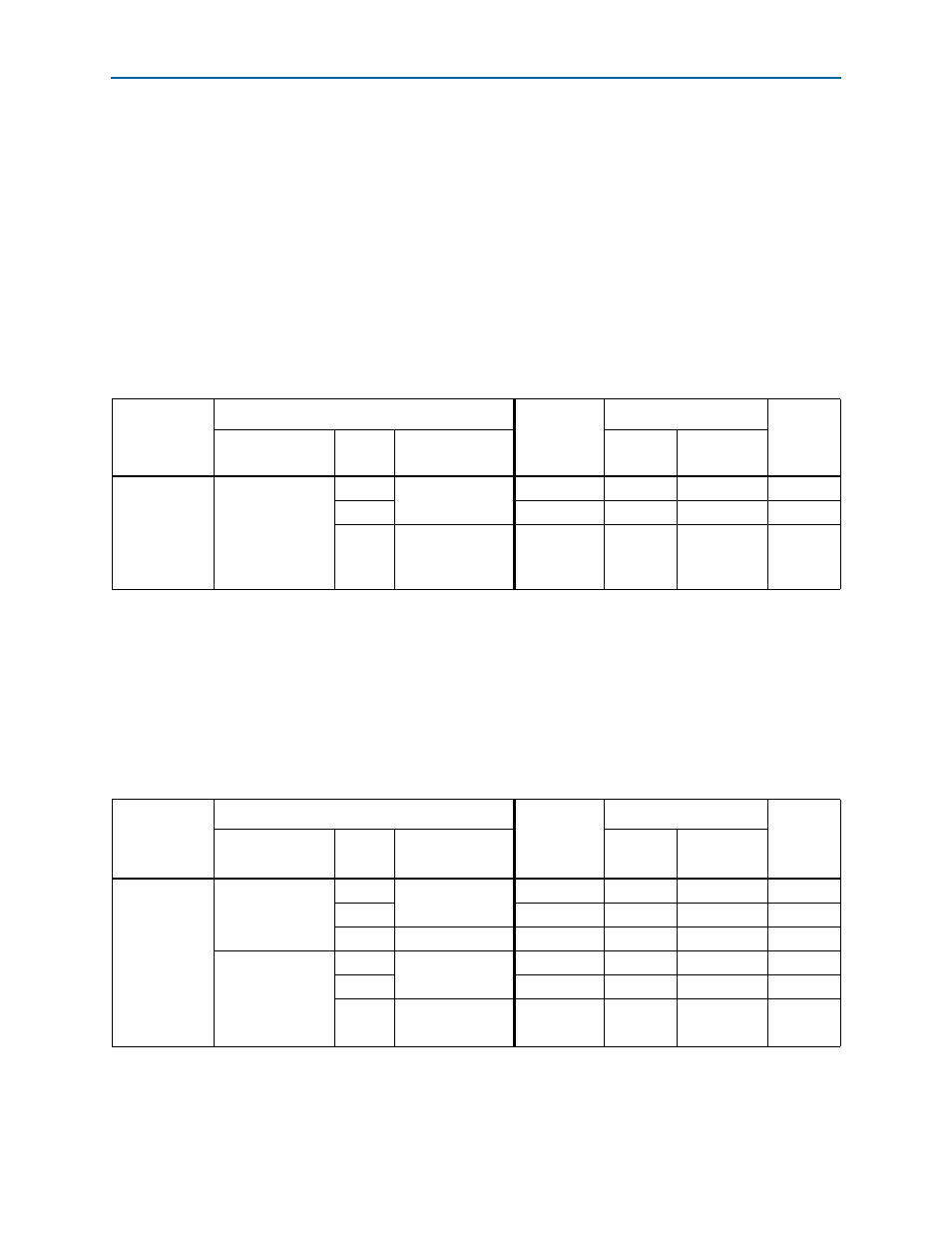

Table 1–3. RapidIO IP Core Arria 10 Resource Utilization

Device

Parameters

ALMs

Registers

Memory

Blocks

(M20K)

Variation

Mode

Baud Rate

(Gbaud)

Primary

Secondary

Arria 10

Physical and

Transport layers,

I/O master and

slave, and

Maintenance

master and slave

1x

5.00

10000

12500

800

79

2x

11600

15400

900

70

4x

3.125

11300

15200

900

70

Table 1–4. RapidIO IP Core 28-nm Device Resource Utilization (Part 1 of 2)

Device

Parameters

ALMs

Registers

Memory

Blocks

(M10K or

M20K

(1)

)

Variation

Mode

Baud Rate

(Gbaud)

Primary

Secondary

Arria V GX

Physical layer only

1x

5.00

4300

6000

336

35

2x

4600

6100

413

35

4x

3.125

4300

6000

352

35

Physical and

Transport layers,

and

I/O master and

slave

1x

5.00

5300

7100

540

56

2x

7400

10000

654

59

4x

3.125

7000

9800

621

59