Reset requirements for arria 10 variations, Reset requirements for arria 10 variations –9 – Altera RapidIO MegaCore Function User Manual

Page 55

Chapter 4: Functional Description

4–9

Clocking and Reset Structure

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

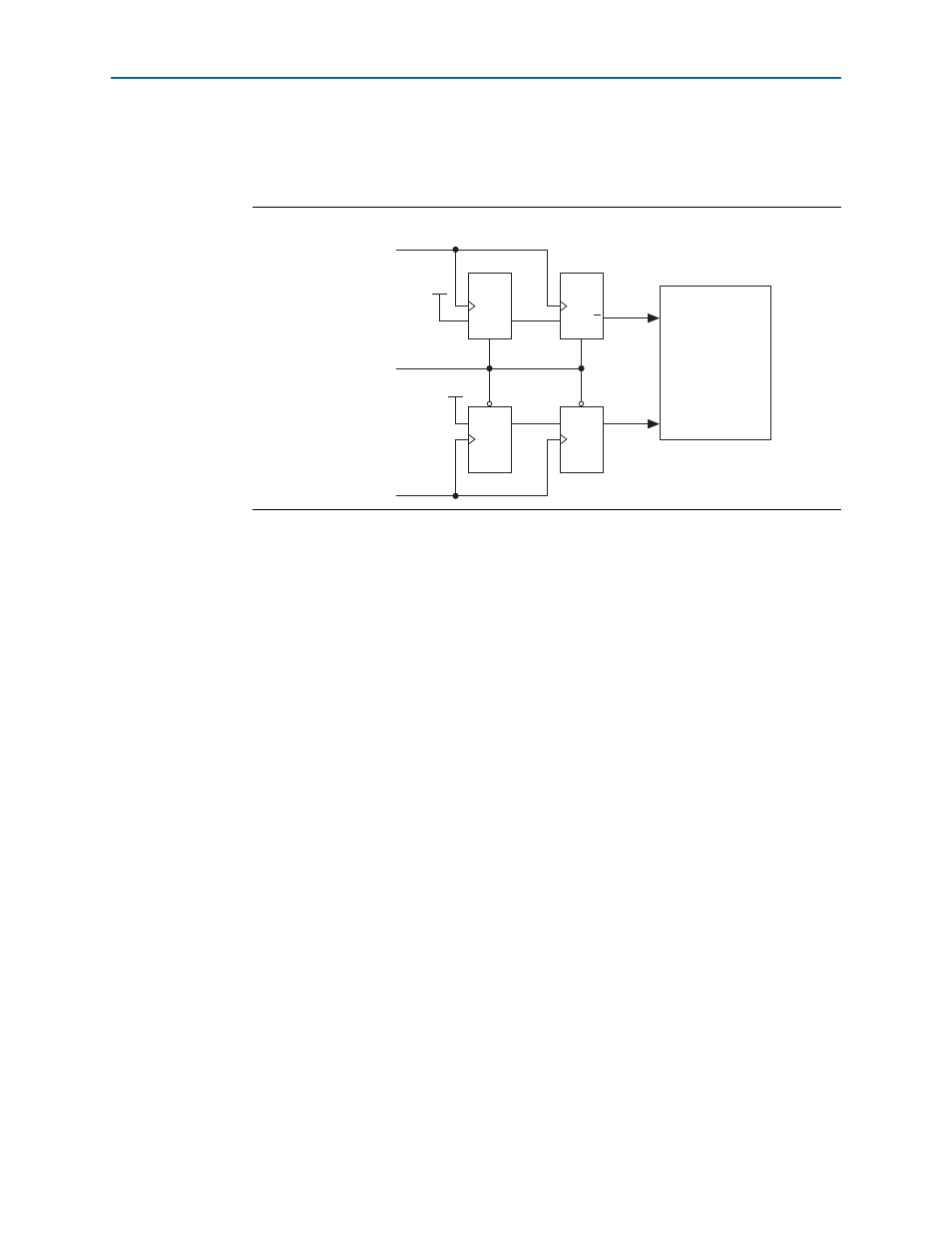

In Arria V, Cyclone V, and Stratix V devices, phy_mgmt_clk_reset must be asserted

with reset_n. However, each signal is deasserted synchronously with its

corresponding clock.

Figure 4–4

shows a circuit that ensures these conditions.

In systems generated by Qsys, this circuit is generated automatically. However, if

your Arria V, Cyclone V, or Stratix V RapidIO IP core variation is not generated by

Qsys, you must implement logic to ensure that reset_n and phy_mgmt_clk_reset are

driven from the same source, and that each meets the minimal hold time and

synchronous deassertion requirements.

For more information about the requirements for reset signals, refer to

Reset Requirements for Arria 10 Variations

To implement the reset sequence correctly for your RapidIO IP core configured on an

Arria 10 device, you must connect the tx_analogreset, tx_digitalreset,

rx_analogreset

, and rx_digitalreset signals to an Altera Transceiver PHY Reset

Controller IP core. User logic must drive the following signals from a single reset

source:

■

RapidIO IP core reset_n (active low) input signal.

■

Transceiver PHY Reset Controller reset (active high) input signal.

■

TX PLL mcgb_rst

(active high) input signal. However, Arria 10 device

requirements take precedence. Depending on the TX PLL configuration, your

design might need to drive TX PLL mcgb_rst with different constraints.

User logic must connect the remaining input reset signals of the RapidIO IP core to the

corresponding output signals of the Transceiver PHY Reset Controller IP core.

f

For information about the Altera Transceiver PHY Reset Controller IP core, refer to

.

Figure 4–4. Circuit to Also Ensure Synchronous Assertion of phy_mgmt_clk_reset with reset_n

D

D

Q

Q

rst_n

rst_n

V

CC

sysclk

phy_mgmt_clk

rst

reset_n

RapidIO

IP Core

D

D

Q

Q

rst

rst

V

CC

phy_mgmt_clk_reset