Altera RapidIO MegaCore Function User Manual

Page 119

Chapter 5: Signals

5–5

Physical Layer Signals

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

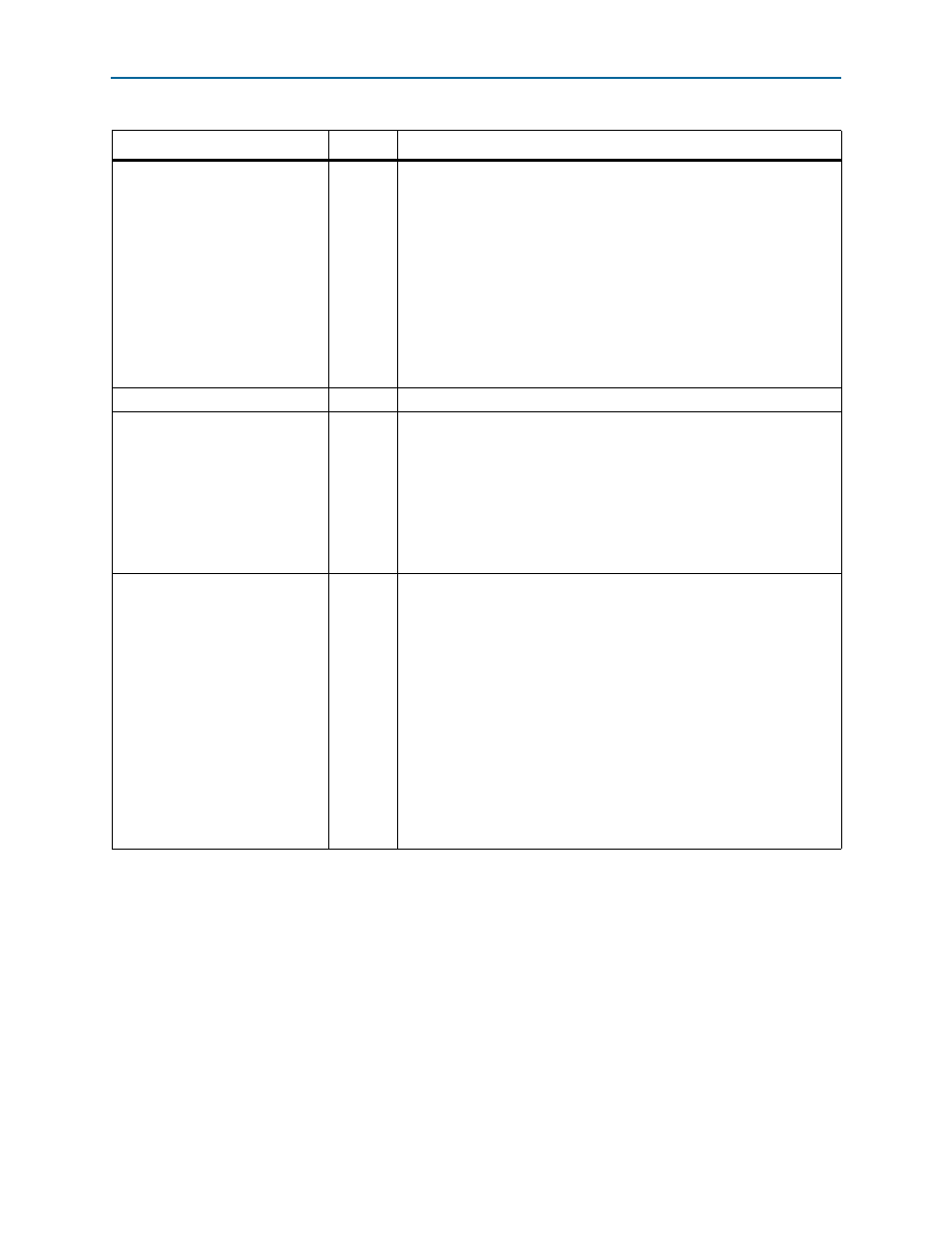

phy_mgmt_clk_reset

Input

Resets the Custom PHY IP core. This signal is present only in Arria V,

Cyclone V, and Stratix V variations.

phy_mgmt_clk_reset

can be asserted asynchronously, but must stay

asserted at least one clock cycle and must be de-asserted synchronously

with phy_mgmt_clk. In addition, this signal must be driven by the same

source as reset_n, to ensure that the two signals are asserted—but not

deasserted—together. Refer to

for a circuit that

shows how to enforce the synchronous assertion with reset_n and the

minimal removal time and synchronous deassertion with phy_mgmt_clk.

In addition, phy_mgmt_clk_reset should not be deasserted when the

Altera Transceiver Reconfiguration Controller reconfig_busy signal is

high.

rxgxbclk

Output

Transceiver receiver clock (recovered clock).

reconfig_clk

(2)

Input

Reference clock for the dynamic reconfiguration controller. The frequency

range for this clock is 2.5–50 MHz. If you use a dynamic reconfiguration

block in your design to dynamically control the transceiver, then this clock

is required by the dynamic reconfiguration block and the RapidIO IP core.

If no external dynamic reconfiguration block is used, this input should be

tied low.

This signal is not present in Arria V, Arria 10, Cyclone V, or Stratix V

variations.

reconfig_togxb

(2)

Input

Driven from an external dynamic reconfiguration block. Supports the

selection of multiple transceiver channels for dynamic reconfiguration.

Note that not using a dynamic reconfiguration block that enables offset

cancellation results in a non-functional hardware design.

In Arria V, Cyclone V, and Stratix V devices, the width of this bus is (C + 1)

× 70, where C is the number of channels, 1, 2, or 4. This width supports

communication from an Altera Reconfiguration Controller with C + 1

reconfiguration interfaces—one dedicated to each channel and another for

the transceiver PLL—to the transceiver.

If you omit the Altera Reconfiguration Controller from your simulation

model, you must ensure all bits of this bus are tied to 0. For more

information about the Altera Reconfiguration Controller component, refer

.

This signal is not present in Arria 10 variations.

Table 5–8. Transceiver Signals (Part 2 of 4)

Signal Direction

Description