Altera RapidIO MegaCore Function User Manual

Page 135

Chapter 6: Software Interface

6–3

August 2014

Altera Corporation

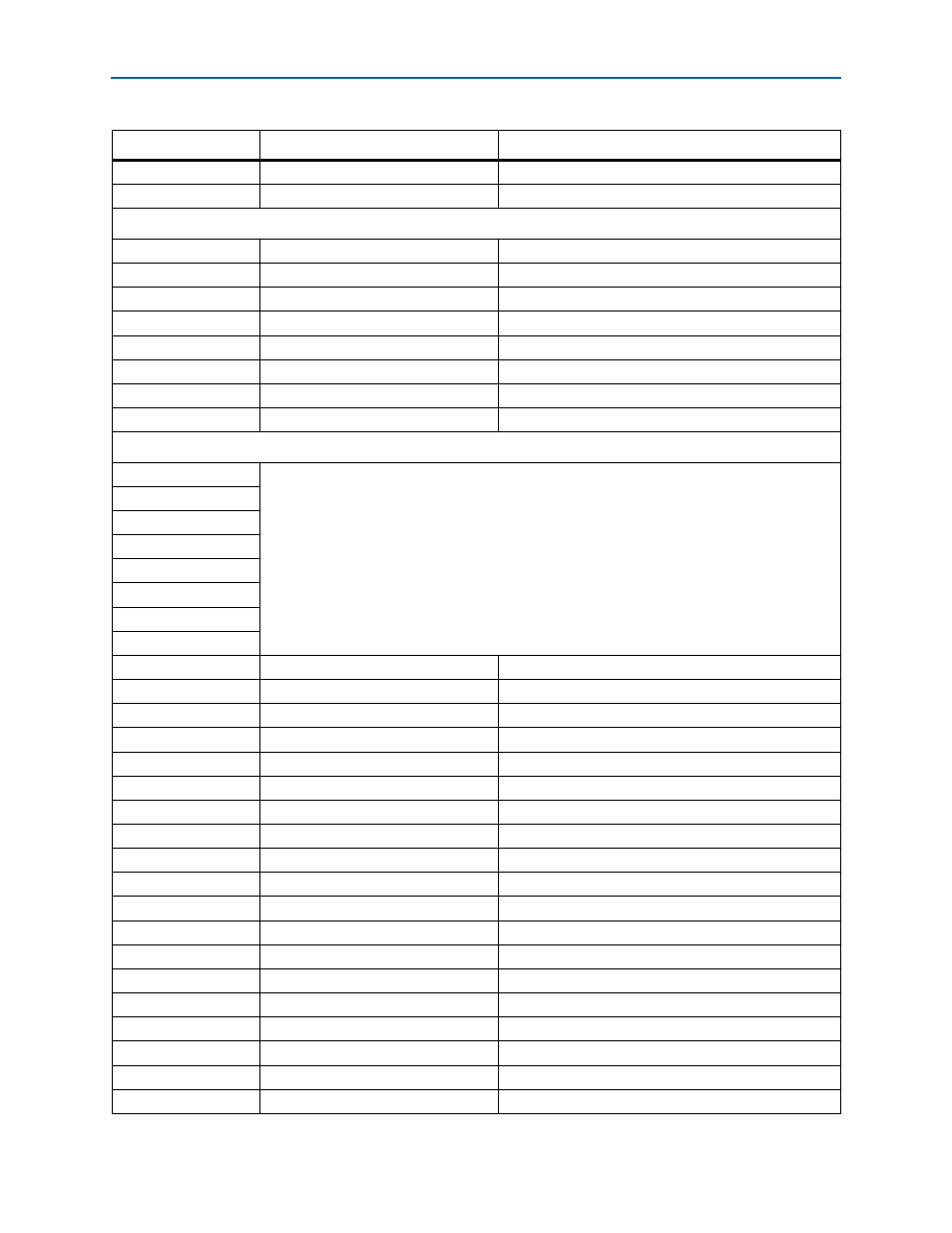

RapidIO MegaCore Function

User Guide

0x68

Host

Base Device ID Lock

Maintenance module

0x6C

Component

Tag

Accessed via the Maintenance module

Extended Features Space

0x100

Register

Block Header

Physical layer

0x104–0x11C

Reserved

—

0x120

Port

Link Time-out Control

Logical layer modules

0x124

Port

Response Time-out Control

Logical layer modules

0x13C

Port

General Control

Physical layer

0x148

Port 0 Local AckID

Physical layer

0x158

Port 0 Error

and Status

Physical layer

0x15C

Port 0 Control

Physical layer

Implementation-Defined Space

0x10000

Reserved

0x10004

0x10008

0x1000C–0x1001C

0x10020

0x10024

0x10028

0x1002C-0x1007C

0x10080

Maintenance

Interrupt

Maintenance module

0x10084

Maintenance

Interrupt Enable

Maintenance module

0x10088

Rx

Maintenance Mapping

Maintenance module

0x1008C–0x100FC

Reserved

—

0x10100

Tx

Maintenance Window 0 Base

Maintenance module

0x10104

Tx

Maintenance Window 0 Mask

Maintenance module

0x10108

Tx Maintenance

Window 0 Offset

Maintenance module

0x1010C

Tx

Maintenance Window 0 Control

Maintenance module

0x10110–0x101FC

Tx

Maintenance Windows 1-15

Maintenance module

0x10200

Tx

Port Write Control

Maintenance module

0x10204

Tx

Port Write Status

Maintenance module

0x10210–0x1024C

Tx

Port Write Buffer

Maintenance module

0x10250

Rx

Port Write Control

Maintenance module

0x10254

Rx

Port Write Status

Maintenance module

0x10260–0x1029C

Rx

Port Write Buffer

Maintenance module

0x102A0–0x102FC

Reserved

—

0x10300

I/O

Master Window 0 Base

Input/Output Master Logical layer

0x10304

I/O

Master Window 0 Mask

Input/Output Master Logical layer

0x10308

I/O

Master Window 0 Offset

Input/Output Master Logical layer

Table 6–2. Memory Map (Part 2 of 3)

Address

Name

Used by