Additional information, Document revision history – Altera RapidIO MegaCore Function User Manual

Page 193

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

Additional Information

This chapter provides additional information about the document and Altera.

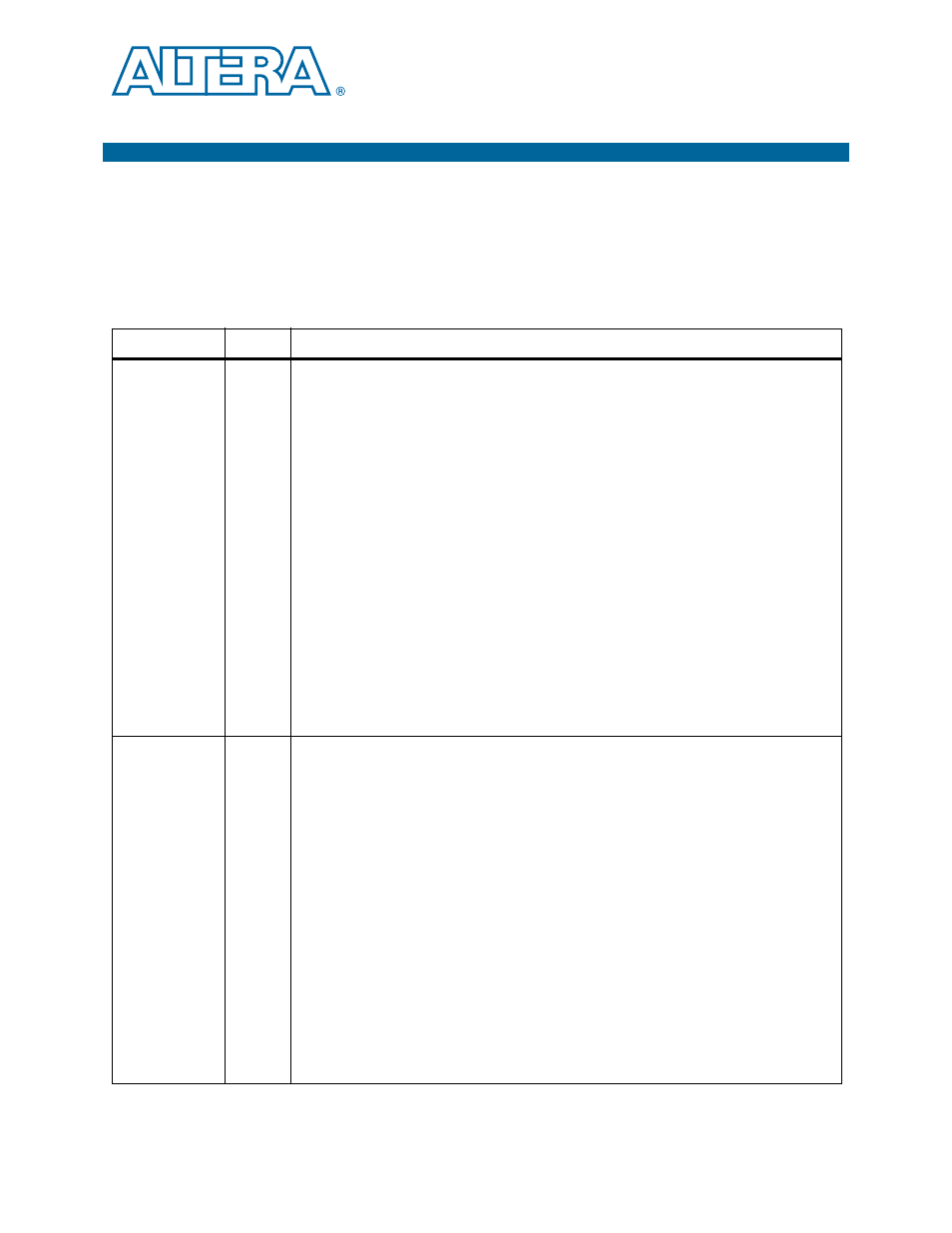

Document Revision History

The following table shows the revision history for this user guide.

Date

Version

Changes

August 2014

14.0

Arria 10

Edition

■

Added support for Arria 10 devices:

■

New parameter Enable transceiver dynamic reconfiguration allows you to hide or

make visible the Arria 10 Native PHY IP core dynamic reconfiguration interface, an

Avalon-MM interface for programming the hard registers in the Arria 10 transceiver.

Information added in

,

“Clocking and Reset Structure” on

, and

■

New requirement to include TX PLL IP core in the Arria 10 design. RapidIO IP core has

new individual transceiver channel clock signals tx_bonded_clocks_chN to connect

to an ATX PLL to support PLL sharing across the transceiver block. Information added

in

,

“Clocking and Reset Structure” on page 4–3

and

.

■

New requirement to include a reset controller in the Arria 10 design. RapidIO IP core

has new transceiver reset signals tx_analogreset, rx_analogreset,

tx_digitalreset

, and rx_digitalreset to connect to the reset controller.

■

Only certain IP core variations support Arria 10 devices. Refer to

“Upgrading a RapidIO Design to the Arria 10 Device Family” on page C–1

for information about the supported and unsupported IP core variations.

■

Updated migration information for the v14.0 Arria 10 Edition software release in

Appendix C, Porting a RapidIO Design from the Previous Version of the Software

.

June 2014

Continued on

next page

14.0

■

Removed device support, resource utilization numbers, and speed grade information for

the following device families that the Quartus II software v13.1 and later no longer

supports: Arria GX, Cyclone II, Stratix II, and Stratix II GX device families.

■

Removed device support for the following HardCopy device families: HardCopy II,

HardCopy III, HardCopy IV E, and HardCopy IV GX device families. This device support

was removed in the 13.1 release.

■

Removed device support, resource utilization numbers, and speed grade information for

the following device families that the Quartus II software v14.0 and later no longer

supports: Cyclone III, Cyclone III LS, and Stratix III device families.

■

Renamed and reordered resource utilization tables in

section.

■

Replaced “Serial RapidIO” with “RapidIO”. The RapidIO IP core supports only the Serial

RapidIO specification, since before the Quartus II software release 8.0 in 2008.

■

Modified

Chapter 2, Getting Started

to describe the new Quartus II software v14.0 IP

design flow.

■

Updated migration information for the v14.0 software release in

RapidIO Design from the Previous Version of the Software

.