Altera RapidIO MegaCore Function User Manual

Page 128

5–14

Chapter 5: Signals

Transport and Logical Layer Signals

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

describes the Avalon-ST pass-through interface transmission (Tx) signals.

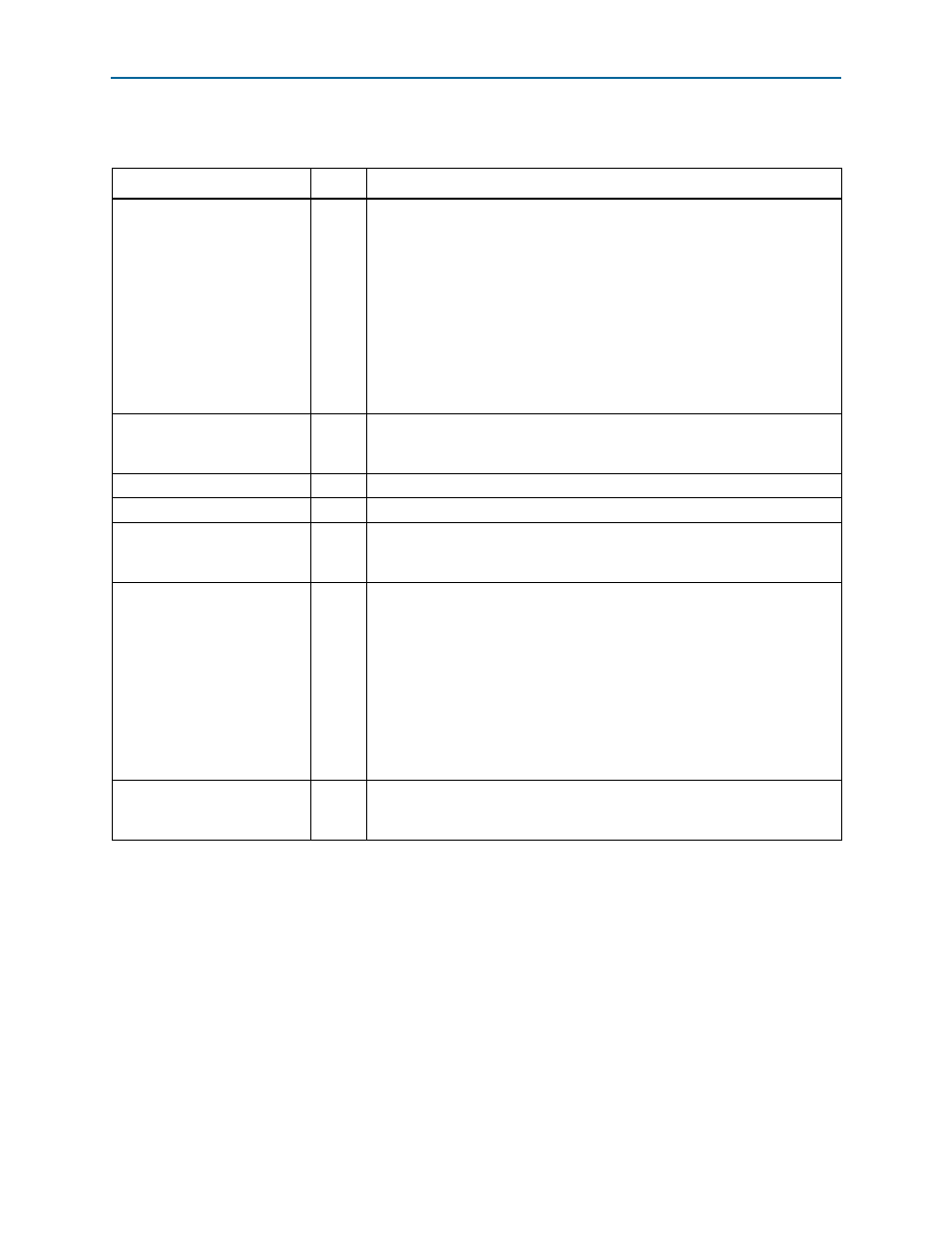

Table 5–19. Avalon-ST Pass-Through Interface Transmission Signals

Signal Type

Function

gen_tx_ready

Output

Indicates that the IP core is ready to receive data on the next clock cycle.

Asserted by the Avalon-ST sink to mark ready cycles, which are the cycles in

which transfers can take place. If ready is asserted on cycle N, the cycle

(N+READY_LATENCY) is a ready cycle.

In the RapidIO IP core, READY_LATENCY is equal to 1, so the cycle immediately

following the rising clock edge on which gen_tx_ready is detected as asserted

is the ready cycle.

This signal may alternate between 0 and 1 when the Avalon-ST pass-through

transmitter interface is idle. After gen_tx_valid is asserted, gen_tx_ready

remains asserted for the duration of the packet transmission, unless the

Physical layer transmit buffer fills.

gen_tx_valid

Input

Used to qualify all the other transmit side of the Avalon-ST pass-through

interface input signals. On every ready cycle in which gen_tx_valid is high,

data is sampled by the IP core.

gen_tx_startofpacket

Input

Marks the active cycle containing the start of the packet.

gen_tx_endofpacket

Input

Marks the active cycle containing the end of the packet.

gen_tx_data

Input

A 32-bit wide data bus for 1x variations, or a 64-bit wide data bus for 2x or 4x

variations. Carries the bulk of the information transferred from the source to the

sink.

gen_tx_empty

Input

This bus identifies the number of empty bytes on the last data transfer of the

gen_tx_endofpacket

. For a 32-bit wide data bus, this bus is 2 bits wide. For a

64-bit wide data bus, this bus is 3 bits wide. The least significant bit is ignored

and assumed to be 0. The following values are supported:

32-bit bus:

2'b0X

none

2'b1X

[15:0]

64-bit bus:

3'b00X

none

3'b01X [15:0]

3'b10X [31:0]

3'b11X [47:0]

gen_tx_error

Input

If asserted any time during the packet transfer, this signal indicates the

corresponding data has an error and causes the packet to be dropped by the IP

core. A value of zero on any beat indicates the data on that beat is error-free.

:

(1) gen_tx_valid is used to qualify all the other input signals of the transmit side of the Avalon-ST pass-through interface.