Altera RapidIO MegaCore Function User Manual

Page 184

8–10

Chapter 8: Qsys Design Example

Running Qsys

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

Refer to

to ensure that you connected the ports correctly.

1

“Reset for RapidIO IP Cores” on page 4–7

, the circuitry necessary to

ensure the correct behavior of the reset_n input signal to the RapidIO IP core is

created automatically by Qsys. For this design example, you do not implement the

logic described in

, because Qsys implements it for you.

The remaining errors are resolved as you modify the slave port base addresses, as

described in the following section.

Assigning Addresses and Setting the Clock Frequency

To assign a specific address, follow these steps:

1. Click on the address that you want to change in the Base column, then type the

address that you want to assign. Make the address assignments specified in

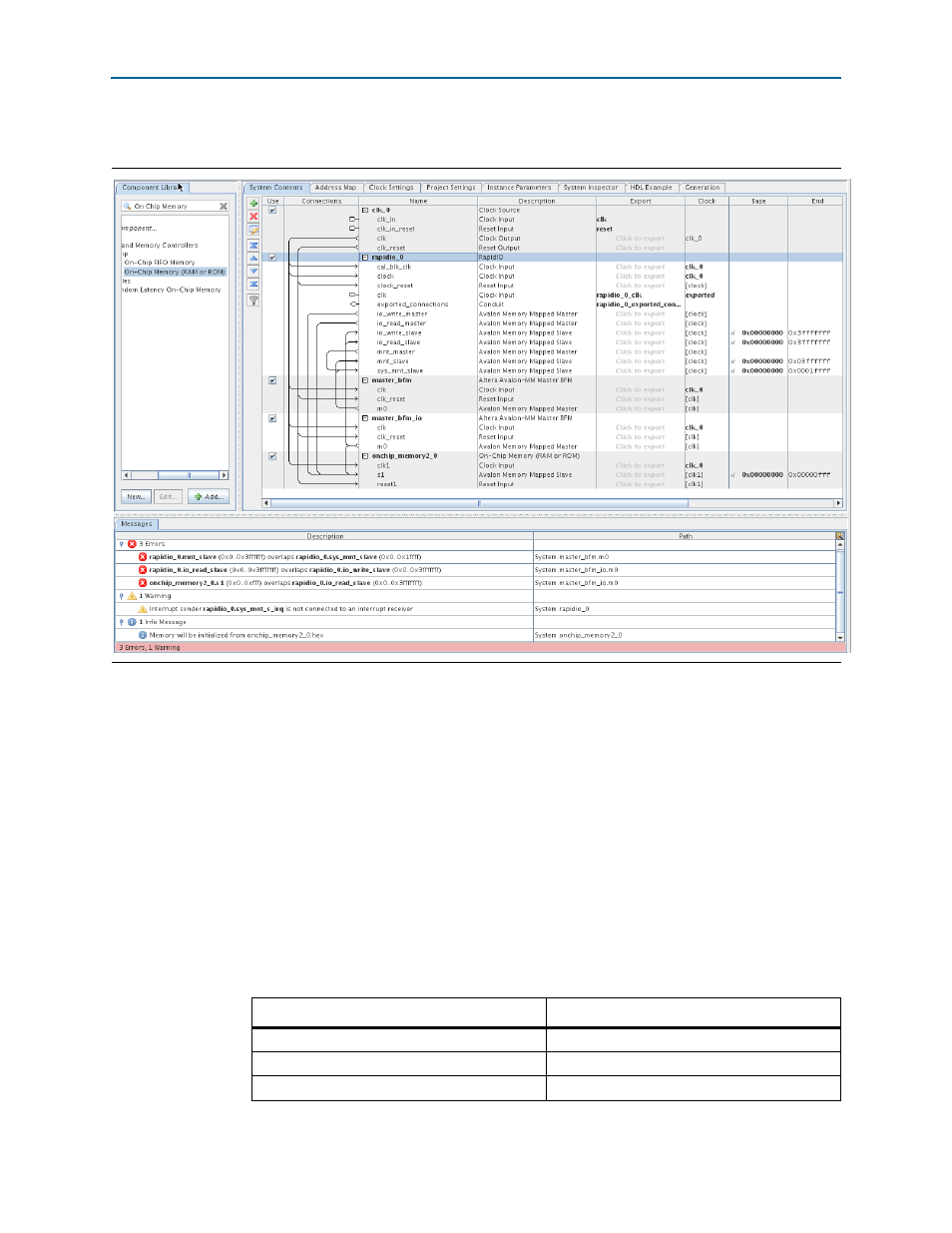

Figure 8–3. Complete System Connections

Table 8–7. Assign Addresses (Part 1 of 2)

Port Name

Base Address

rapidio_0 io_write_slave

0x40000000

rapidio_0 io_read_slave

0x80000000

rapidio_0 mnt_slave

0x04000000