Nwrite transactions, Nwrite transactions –7 – Altera RapidIO MegaCore Function User Manual

Page 169

Chapter 7: Testbenches

7–7

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

Initially, the testbench performs two single word transfers, writing to an even word

address first and then to an odd word address. The testbench then generates a

predetermined series of burst writes across the Input/Output Avalon-MM slave

module's Avalon-MM write interface on the DUT. These write bursts are each

converted into NWRITE_R request packets sent over the RapidIO Serial interface. The

testbench cycles from 8 to MAX_WRITTEN_BYTES in steps of 8 bytes. Two tasks are

invoked to carry out the burst writes, rw_addr_data and rw_data. The rw_addr_data

task initiates the burst and the rw_data task completes the burst.

At the sister_rio module, the NWRITE_R request packets are received and presented

across the I/O master Avalon-MM interface as write transactions. The testbench calls

the read_writedata task of the sister_bfm_io_write_slave module. The task captures

the written data. The written data is checked against the expected value.

In addition, the test checks that the NWRITE_RS_COMPLETED interrupt field of the

Input/Output Slave Interrupt

register is set, then clears the field, and checks again

to confirm the field was cleared correctly.

NWRITE Transactions

To perform NWRITE operations, one register in the IP core must be reconfigured as

shown in

. With these settings, any write operation presented across the

Input/Output Avalon-MM slave interface is translated into a RapidIO NWRITE

transaction.

Initially, the testbench performs two single word transfers, writing to an even word

address first and then to an odd word address. The testbench then generates a

predetermined series of burst writes across the Input/Output Avalon-MM slave

module's Avalon-MM write interface on the DUT. These write bursts are each

converted into an NWRITE request packet that is sent over the RapidIO serial interface.

The testbench cycles from 8 to MAX_WRITTEN_BYTES in steps of 8 bytes. Two tasks are

run to carry out the burst writes, rw_addr_data and rw_data. The rw_addr_data task

initiates the burst and the rw_data task completes the remainder of the burst.

The sister_rio module receives the NWRITE request packets and presents them across

the I/O master Avalon-MM slave interface as write transactions. The testbench calls

the read_writedata task of the sister_bfm_io_write_slave module. The task captures

the written data. The written data is checked against the expected value.

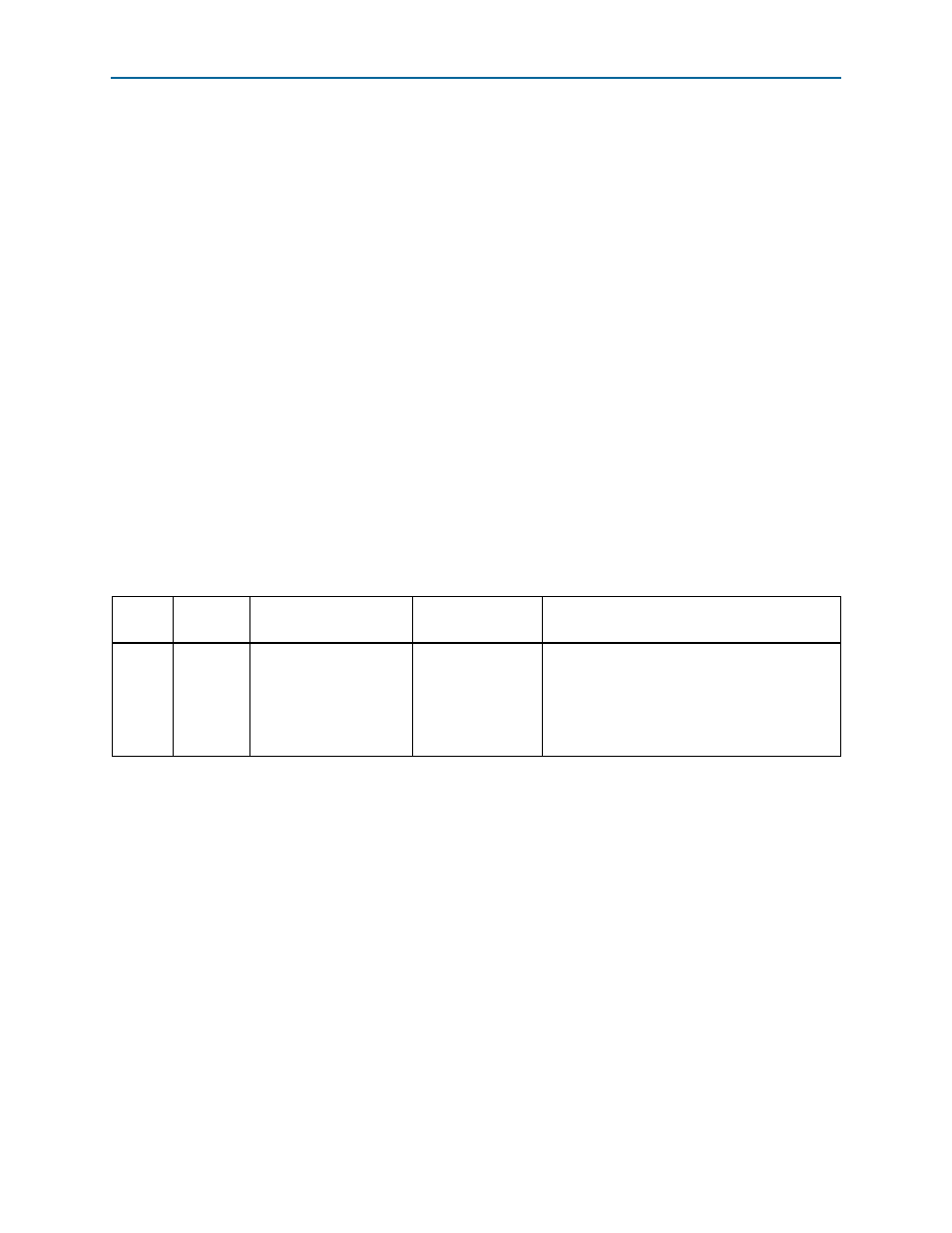

Table 7–4. NWRITE Transactions

Module

Register

Address

Name

Value

Description

rio

0x1040C

Input/Output Slave

Mapping Window

0

Control

32'h0055_0000

or

32'h5555_0000

Sets the DESTINATION_ID for outgoing

transactions to the value 0x55 or 0x5555,

depending on the device ID width of the

sister_rio. This value matches the base device ID

of the sister_rio. Sets the write request type back

to NWRITE.