Physical layer architecture, Physical layer architecture –11, Error management – Altera RapidIO MegaCore Function User Manual

Page 57: Clock decoupling, Fifo buffer with level output port, Adjustable buffer sizes (4 kbytes to 32 kbytes)

Chapter 4: Functional Description

4–11

Physical Layer

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

■

Error management

■

Clock decoupling

■

FIFO buffer with level output port

■

Adjustable buffer sizes (4 KBytes to 32 KBytes)

■

Four transmission queues and four retransmission queues to handle packet

prioritization

■

Can be configured to send link-request control symbols with cmd set to

reset-device

on fatal error

■

Attempts link-request link-response control symbol pair a configurable

number of times before declaring fatal error, when a link-response is not received

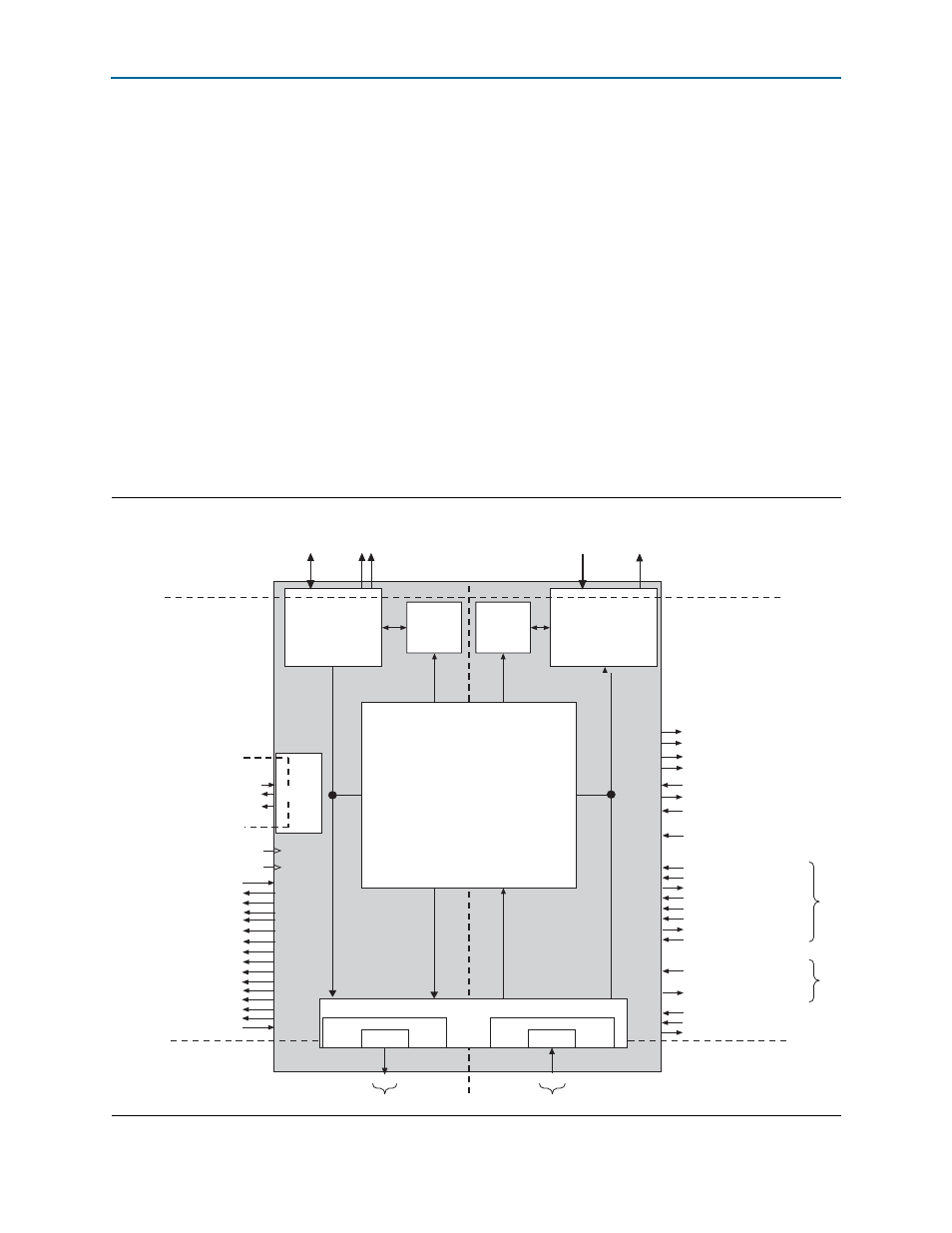

Physical Layer Architecture

shows the architecture of the Physical layer and illustrates the interfaces

that it supports. Dotted lines indicate clock domain boundaries within the layer.

Figure 4–5. Physical Layer High Level Block Diagram

Receive

Buffer

Transmit

Buffer

Control

Receive

Buffer

Control

td

rd

tx_bonding_clocks_chN

clk

reset_n

RapidIO Interface

RapidIO Interface

Transmit

Buffer

buf_av0

atxwl

e

ve

l

arxwl

e

ve

l

packet_transmitted

packet_cancelled

packet_accepted

packet_retry

packet_not_accepted

packet_crc_error

symbol_error

buf_av1

rxclk

atxo

vf

buf_av2

buf_av3

rx_errdetect

gxbpll_locked

char_err

cal_blk_clk or

phy_mgmt_clk_reset

reconfig_clk

reconfig_clk_chN

reconfig_reset_chN

reconfig_waitrequest_chN

reconfig_read_chN

reconfig_write_chN

reconfig_address_chN

reconfig_readdata_chN

reconfig_writedata_chN

{rx,tx}_analogreset

{rx,tx}_digitalreset

{rx,tx}_cal_busy

rx_is_lockedtodata

reconfig_togxb

reconfig_fromgxb

txclk

multicast_event_rx

multicast_event_tx

port_initialized

port_error

ef_ptr[15:0]

port_response_timeout[23:0]

Registers

master_enable

gxb_powerdown

Low Level Interface

Transmitter

Transceiver

Transmitter

Receiver

Transceiver

Receiver

Protocol and Flow Control

Engine

phy_mgmt_clk

(Arria V, Cyclone V,

Stratix V only)

To/From

Tx Transport

Layer

To/From

Rx Transport

Layer

Arria 10

dynamic

reconfiguration

interfaces

Arria 10

only